# Motionnet

RemoteI/O & RemoteMotion

### <u>G9004A</u> (CPU emulation device)

# **User's Manual**

**NPM** Nippon Pulse Motor Co., Ltd.

[Preface]

Thank you for considering our super high-speed serial communicator LSI, the "G9000" series.

To learn how to use the G9000 series device, read this manual and "G9001A/G9002" user's manual to become familiar with the product.

#### [What the Motionnet is]

As a next generation communication system, the Motionnet can construct faster, more volume large scale, wire saving systems than the conventional T-NET systems (conventional LSI product to construct serial communication system by NPM). Further, it has data communication function, which the T-NET does not have, so that the Motionnet can control data control devices such as in the PCL series (pulse train generation LSI made by NPM).

The Motionnet system consists of one center device connected to a CPU bus, and maximum 64 local devices, and they are connected by using cables of two or three conductive cores.

[Cautions]

(1) Copying all or any part of this manual without written approval is prohibited.

- (2) The specifications of this LSI may be changed to improve performance or quality without prior notice.

- (3) Although this manual was produced with the utmost care, if you find any points that are unclear, wrong, or have inadequate descriptions, please let us know.

- (4) We are not responsible for any results that occur from using this LSI, regardless of item (3) above.

[Logic indicators] -

(1) Terminal names and signal names that start with a # use negative logic.

Ex.: #CS means that the CS terminal uses negative logic. This has the same meaning as  $\overline{CS}$ .

| 1. Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1       |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 2. Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1       |

| 3. General specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1       |

| 3-1. Communication system specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 3-1. Specifications of the CPU emulation device (G9004A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ا۱<br>1 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 4. Hardware description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3       |

| 4-1. A list of terminals (QFP-80)<br>4-2. Terminal assignment drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |         |

| 4-2. Terminal assignment drawings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| , and the second se |         |

| 5. Functions of terminals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 5-1. OLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 5-2. #RS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 5-3. #DN0 105                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |         |

| 5-5. #DNSO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-6. SPD0, SPD1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 5-7. TUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 5-8. TMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 5-9. #TOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-10. SO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 5-11. SOEH, #SOEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| 5-12. SOEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-13. SI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9       |

| 5-14. #MRER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9       |

| 5-15. #MSEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| 5-16. BRK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 5-17. MOD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 5-18. LCK0 to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 5-19. LCLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-20. LIF0 to 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |         |

| 5-21. #LRST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| 5-22. #LIFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| 5-23. LA0 to LA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |         |

| 5-24. #LCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-25. #LWR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-20. #LKD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-27. #LWRQ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |         |

| 5-20. #Ented                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |         |

| 5-30. LD8 to LD15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |         |

| 5-31. LWT0 and LWT1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| 5-32. CKSL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |         |

| 5-33. VDD, GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| 6. Setting the status and operation information for the G9004A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 13      |

| 7. Message communication mode (MOD = LOW)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |         |

| 7-1. Terminals for use by a local CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |         |

| 7-2. I/O map for the local CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |

| 7-3. Command and status information that can be used by a local CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |

| 7-3-1. G9004A's commands that can be used by a local CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |         |

| 7-3-2. G9004A status information that can be seen from a local CPU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

#### INDEX

| 7-4. Information command for the center device (G9001A)                             |    |

|-------------------------------------------------------------------------------------|----|

| 7-5. Message communication procedure                                                | 18 |

| 8. CPU emulation mode (MOD = H)                                                     |    |

| 8-1. Terminals on the G9004A                                                        |    |

| 8-2. Control method for using a center device (G9001A)                              | 21 |

| 8-2-1. Command                                                                      |    |

| 8-2-2. Examples of CPU emulation control procedures                                 |    |

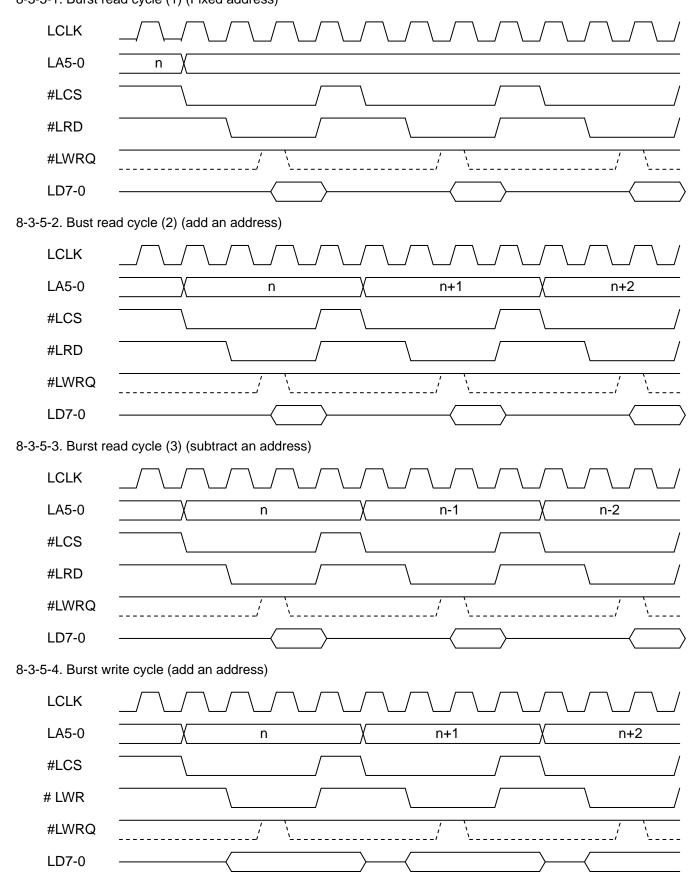

| 8-3. Emulation timing                                                               |    |

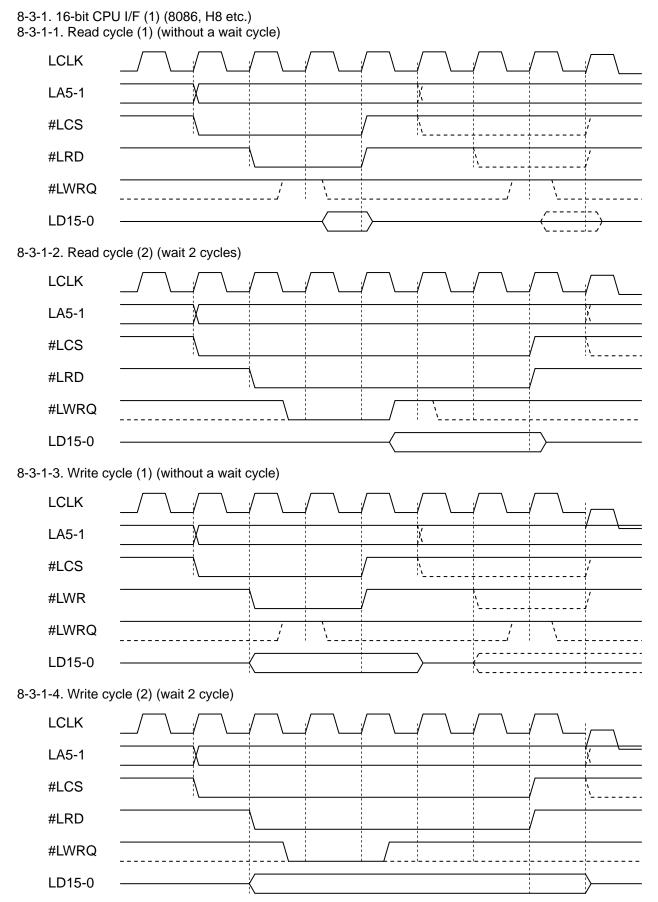

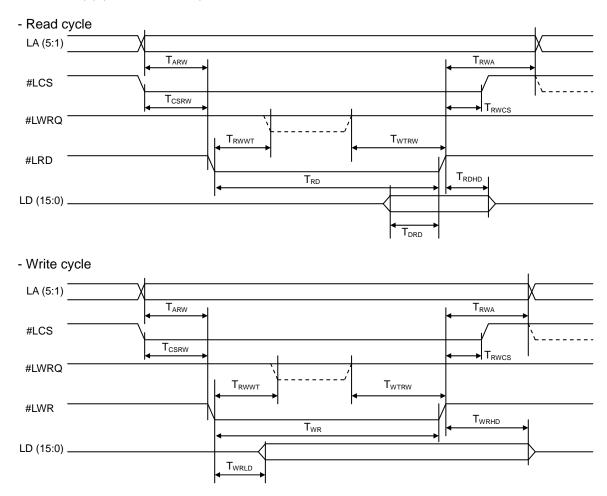

| 8-3-1. 16-bit CPU I/F (1) (8086, H8 etc.)                                           |    |

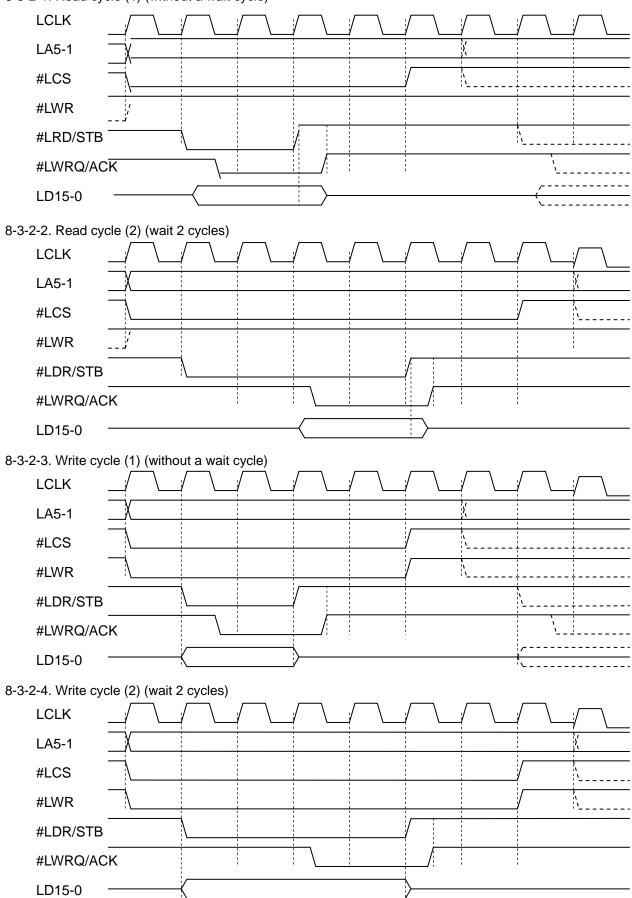

| 8-3-2. 16-bit CPU I/F (2) (68000 etc.)                                              | 31 |

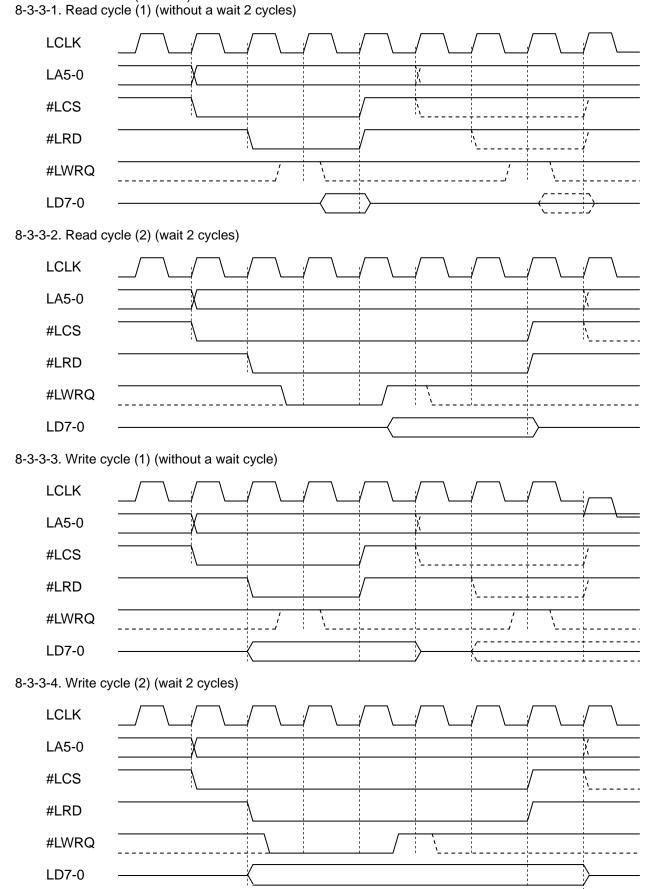

| 8-3-3. 8-bit CPU I/F (Z80 etc.)                                                     | 32 |

| 8-3-4. 8-bit CPU I/F (2) (6809 etc.)                                                |    |

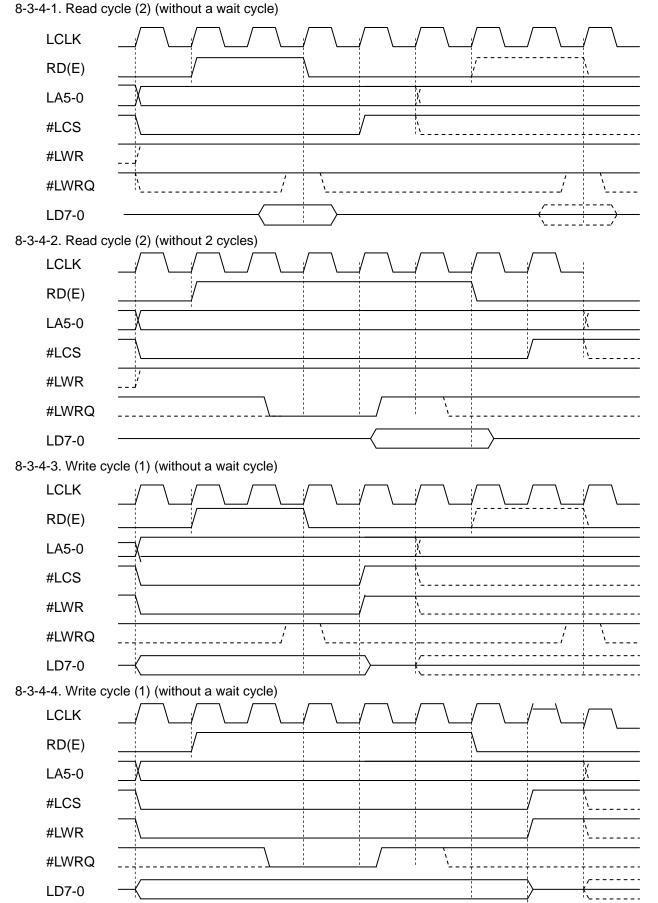

| 8-3-5. Example of a burst cycle (8-bit CPU-I/F (2) (Z80 etc.)                       | 34 |

| 9. Connection examples and recommended environment                                  |    |

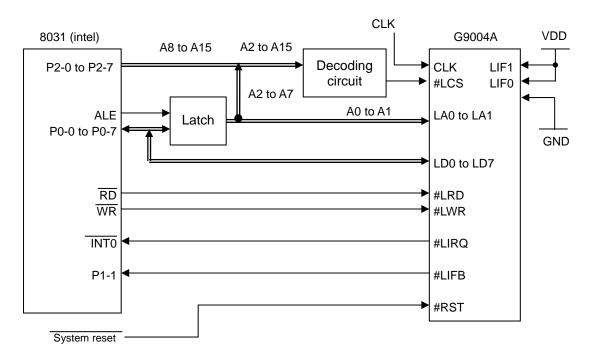

| 9-1. Example of a connection to a CPU using the CPU message communication mode (MOI |    |

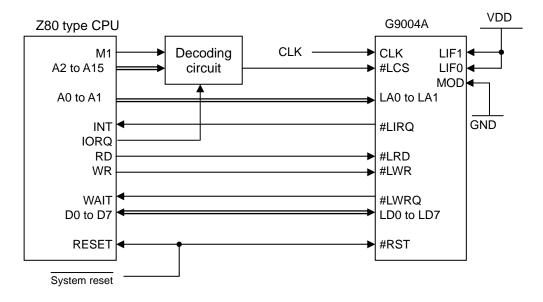

| 9-1-1. 8-bit I/F (1) (IF1 = HIGH, IF0 = HIGH)                                       |    |

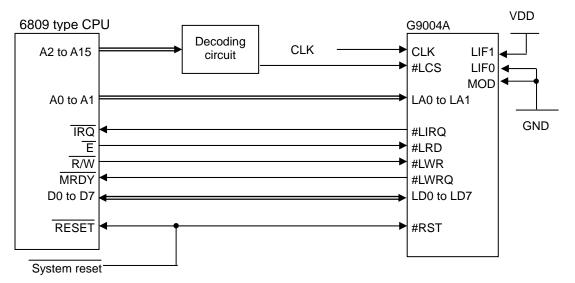

| 9-1-2. 8-bit I/F (2) (IF1 = HIGH, IF0 = LOW)                                        |    |

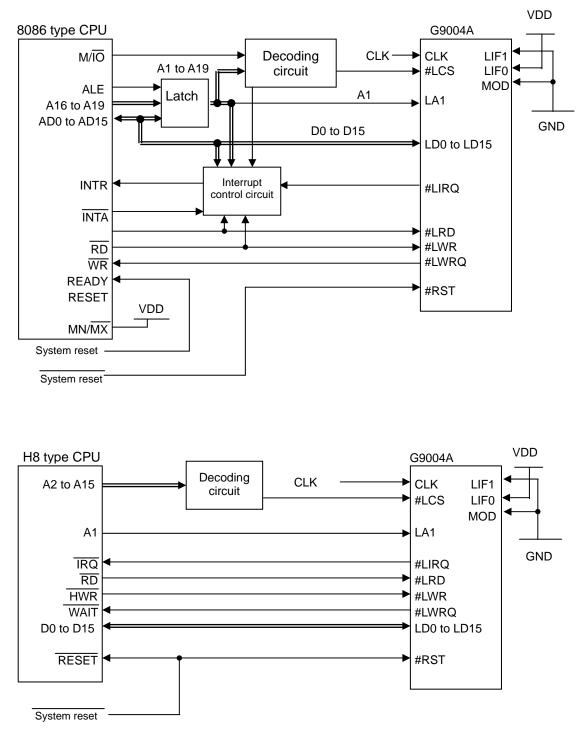

| 9-1-3. 16-bit I/F (1) (IF1=LOW, IF0=HIGH)                                           |    |

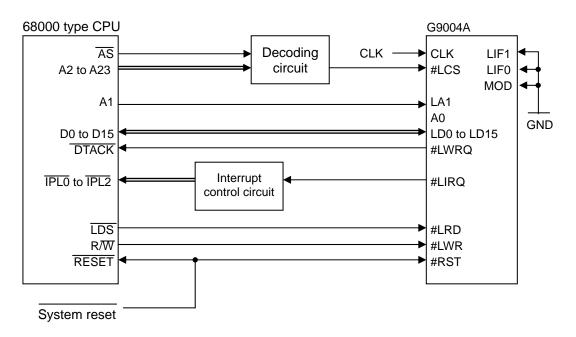

| 9-1-4. 16-bit I/F (2) (IF1 = LOW, IF0 = LOW)                                        |    |

| 9-1-5. Connecting to a CPU without a wait function                                  | 39 |

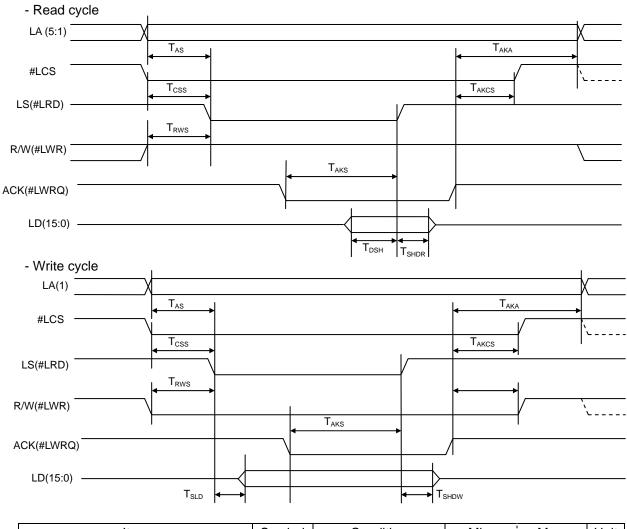

| 9-2. Access timing when the CPU message communication mode is selected (MOD = L)    |    |

| 9-2-1. Normal access                                                                |    |

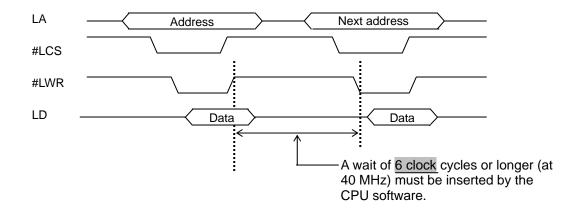

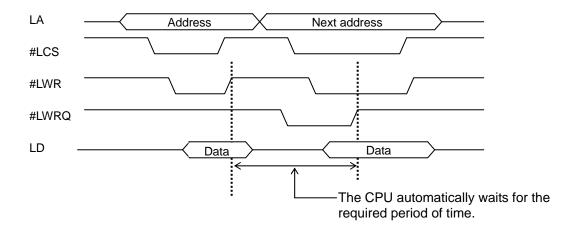

| 9-2-2. Write to command or data transfer FIFO                                       | 40 |

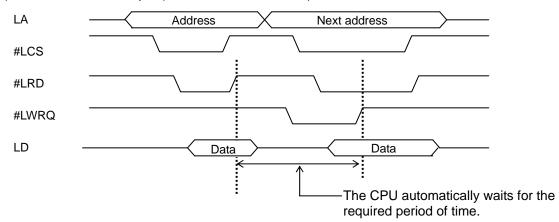

| 9-2-3. Read status                                                                  |    |

| 9-3. Connection to peripheral LSIs when the CPU emulation mode is selected          |    |

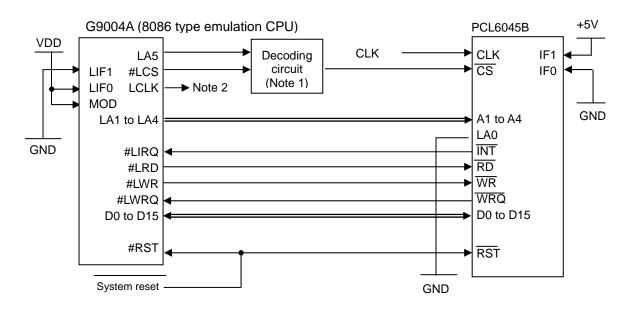

| 9-3-1. Connections to a PCL6045B (8086 type CPU emulation)                          |    |

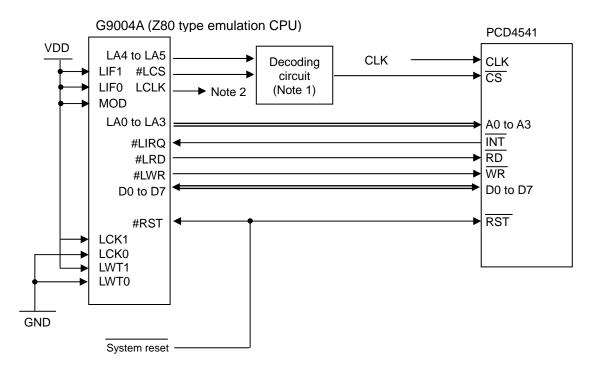

| 9-3-2. Connections to the PCD4541 (Z80 type CPU emulation)                          |    |

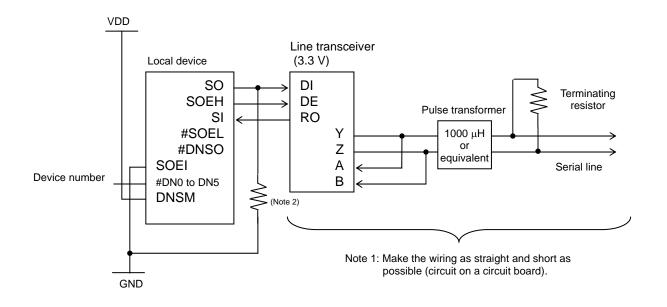

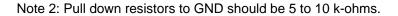

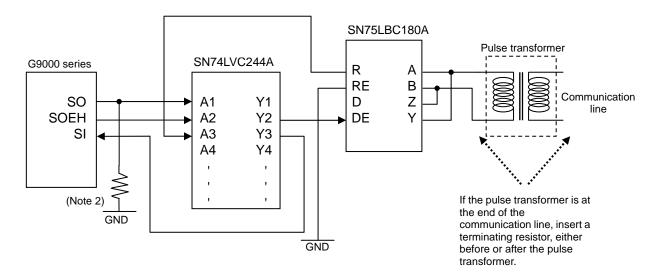

| 9-4. Connections to a serial communication line                                     |    |

| 9-5. A connection example of a level shifter                                        |    |

| 9-6. Complete configuration                                                         |    |

| 9-7. Recommended environment                                                        |    |

| 9-7-1. Cable                                                                        |    |

| 9-7-2. Terminating resistor                                                         |    |

| 9-7-3. Pulse transformer                                                            |    |

| 9-7-4. I/F chip<br>9-7-5. Parts used in our experiments                             |    |

| 9-7-5. Parts used in our experiments                                                |    |

| 9-7-6. Other precautions                                                            | 49 |

| 10. Center device (G9001A)                                                          |    |

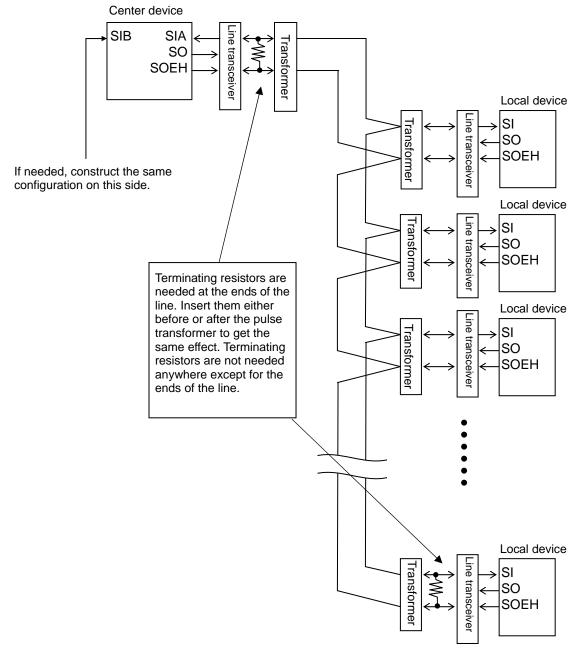

| 10-1. Program example of CPU emulation mode                                         |    |

| 10-1-1. Control example of the PCL6045B                                             |    |

| 10-1-2. Control example of PCD4541                                                  | 53 |

| 11. Electrical characteristics                                                      | 55 |

| 11-1. Absolute maximum ratings                                                      | 55 |

| 11-2. Recommended operating conditions                                              | 55 |

| 11-3. DC characteristics                                                            |    |

| 11-4. AC characteristics                                                            |    |

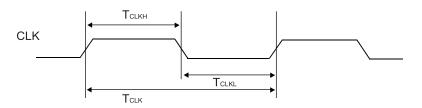

| 11-4-1. System clock                                                                | 56 |

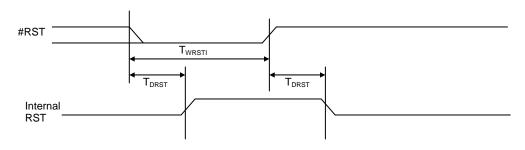

| 11-4-2. Reset timing                                                                |    |

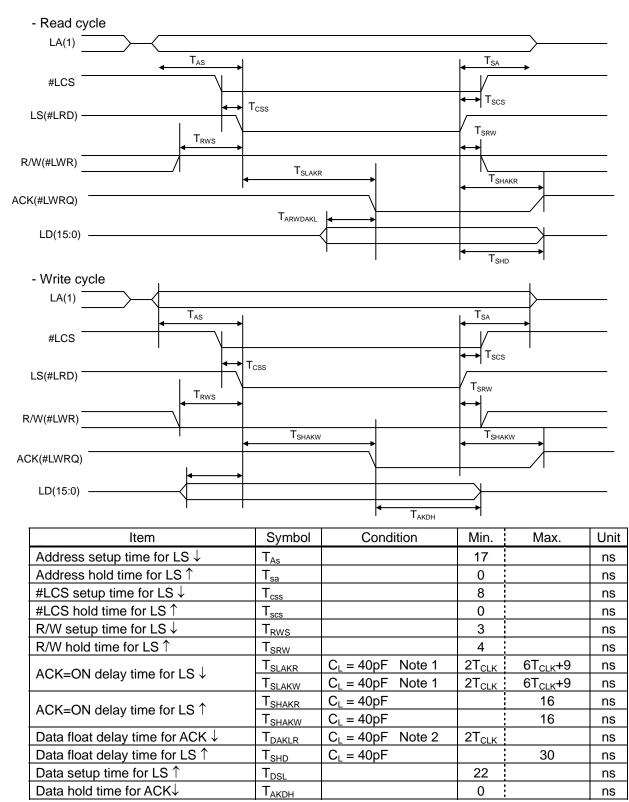

| 11-5. Timing of CPU message communication mode                                      |    |

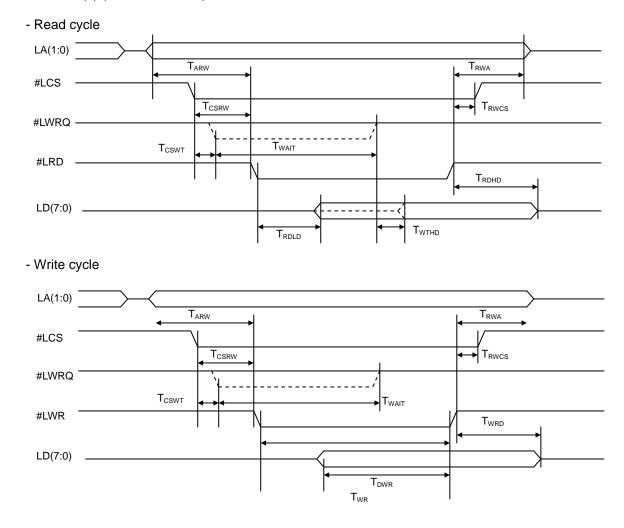

| 11-5-1. 8-bit I/F (1) (IF1 = H, IF0 = H)                                            |    |

| 11-5-2. 8-bit I/F (2) (IF1 = H, IF0 = L)                                            | 58 |

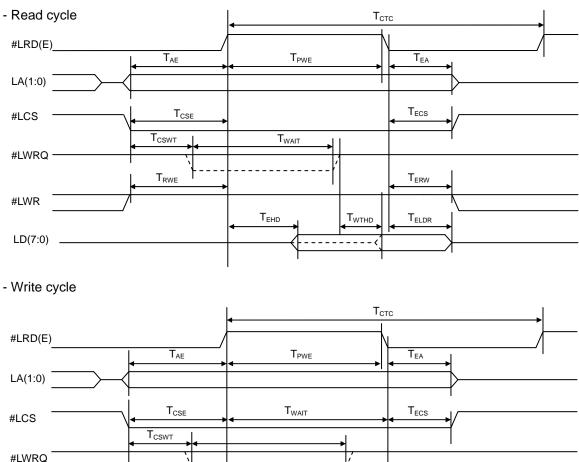

| 11-5-3. 16-bit I/F (1) (IF1 = L, IF0 = H)                                           |    |

| 11-5-4. 16-bit I/F (2) (IF1 = L, IF0 = L)                                           | 60 |

| 11-6. Timing when CPU emulation is selected         | 61 |

|-----------------------------------------------------|----|

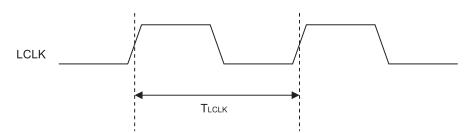

| 11-6-1. LCLK timing                                 | 61 |

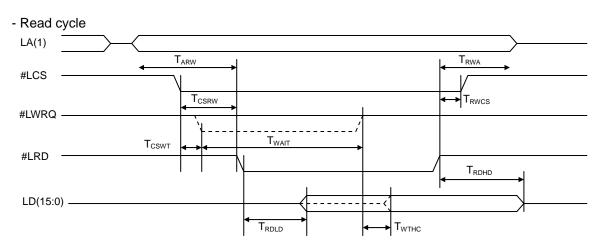

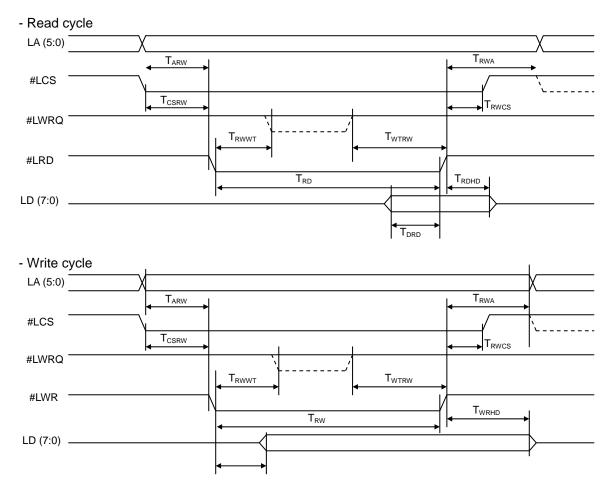

| 11-6-2. 8-bit I/F (1) (IF1 = H, IF0 = H)            |    |

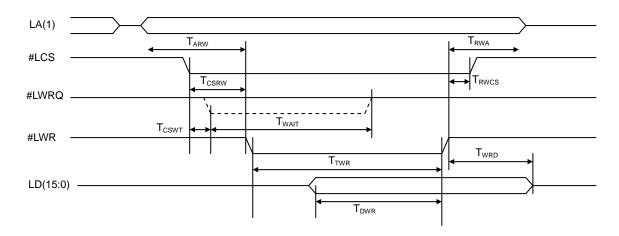

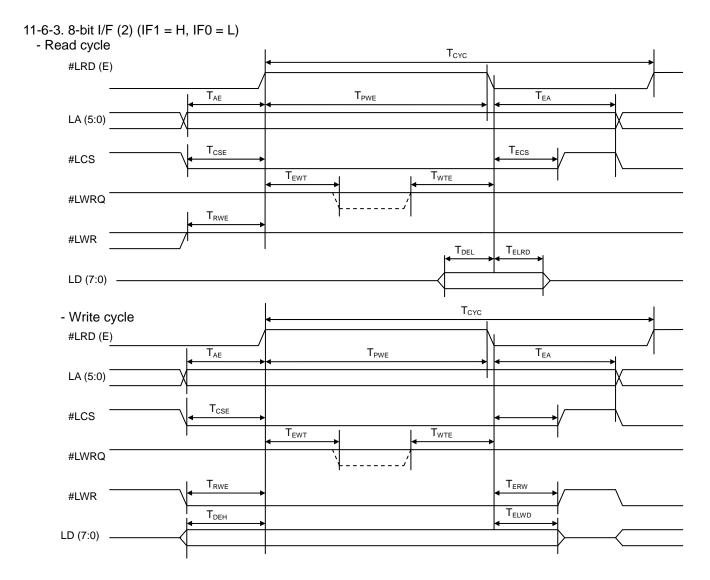

| 11-6-3. 8-bit I/F (2) (IF1 = H, IF0 = L)            | 63 |

| 11-6-4. 16-bit I/F (1) (IF1 = L, IF0 = H)           | 64 |

| 11-6-5. 16-bit I/F (2) (IF1 = L, IF0 = L)           |    |

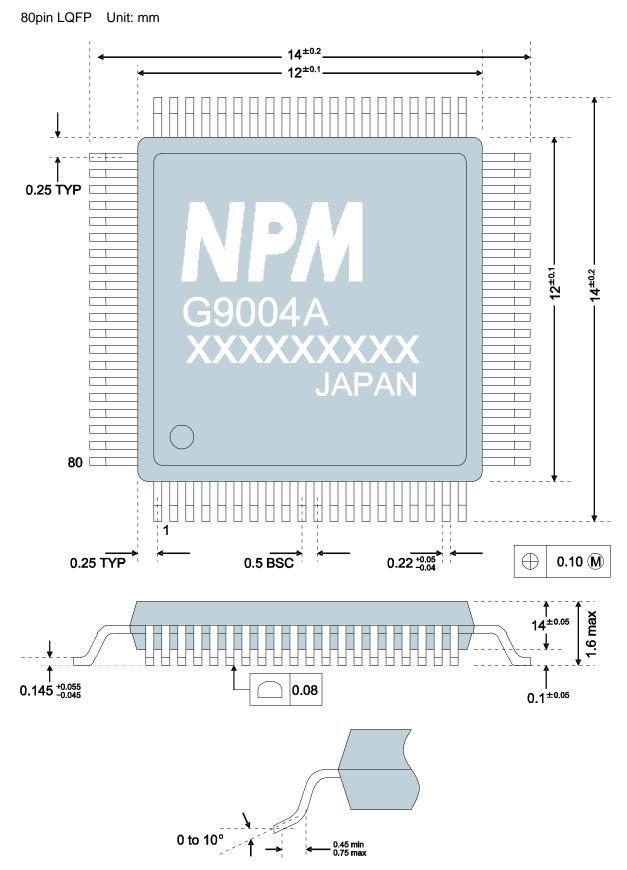

| 12. External dimensions                             | 66 |

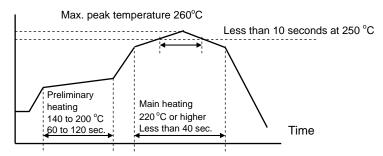

| 13. Handling precautions                            |    |

| 13-1. Design precautions                            | 67 |

| 13-2. Precautions for transporting and storing LSIs |    |

| 13-3. Precautions for mounting                      | 68 |

| 13-4. Other precautions                             | 68 |

|                                                     |    |

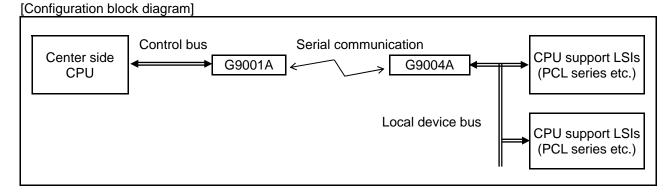

#### 1. Outline

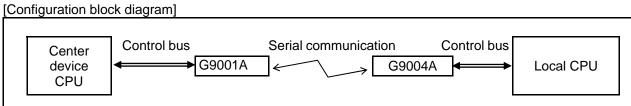

This LSI is a CPU emulation device (G9004A). This LSI can be connected to our Motionnet and perform data communications with a center device (G9001A).

Either of the following two operation modes can be selected from a terminal.

1) CPU emulation mode

In this mode, the G9004A emulates CPU terminal signals using data communicated from the center device (G9001A). Although the communication format from the center device is limited, this LSI outputs signals identical to those from CPU terminals. Therefore it can control various LSIs that are normally connected to a CPU.

2) Message communication mode

One word (16 bits) is reserved by the system in this mode, which is used for communication (the data commands and formats are specified). The user can use the remaining 127 words to communicate data. The format for the message data is not specified, which means that this LSI can communicate freely with almost any CPU that is connected to the center device and to this LSI.

#### 2. Features

- Compatible with our Motionnet.

- Can control various CPU support LSIs using data communications.

- A maximum of 256 bytes of data can be communicated in one sentence.

- A maximum of 64 devices can be connected using one line.

- It has a safety design using a communication failure detection circuit (contains a watchdog timer).

- Powered from just 3.3 VDC.

#### 3. General specifications

#### 3-1. Communication system specifications

| Item                                       | Description                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference clock                            | 40 MHz or 80 MHz                                                                                                                                                                                                                                                                                                         |

| Communication speed                        | 2.5 M, 5 M, 10 M, or 20 Mbps                                                                                                                                                                                                                                                                                             |

| Communication sign                         | NRZ sign                                                                                                                                                                                                                                                                                                                 |

| Communication protocol                     | NPM original method                                                                                                                                                                                                                                                                                                      |

| Communication method                       | Half-duplex communication                                                                                                                                                                                                                                                                                                |

| Communication I/F                          | RS-485 or pulse transfer                                                                                                                                                                                                                                                                                                 |

| Connection method                          | Multi-drop connection                                                                                                                                                                                                                                                                                                    |

| Number of local devices                    | 64 devices max.                                                                                                                                                                                                                                                                                                          |

| Cyclic communication cycle<br>when 20 Mbps | When using 8 local devices<br>(IN: 128 points, OUT: 128 points) 0.12 msec.<br>When using 16 local devices<br>(IN: 256 points, OUT:256 points) 0.24 msec.<br>When using 32 local devices<br>(IN: 512 points, OUT: 512 points) 0.49 msec.<br>When using 64 local devices<br>(IN: 1024 points, OUT: 1024 points) 0.97 msec. |

|                                            | Note: The communication cycle will be extended dependant upon data communication.                                                                                                                                                                                                                                        |

#### 3-2. Specifications of the CPU emulation device (G9004A)

| Item                          | Description                                                                 |

|-------------------------------|-----------------------------------------------------------------------------|

| CPU emulation mode            |                                                                             |

| Communication sentence        | 1 to 128 words/frame (1 word = 16 bits)                                     |

| length                        |                                                                             |

| Data buffer size              | 128 words                                                                   |

| Data communication time       | When communicating 5 words (write to one register in the PCL): 21.7 $\mu s$ |

| Data transfer method          | Status: Cyclic transfer, Data: Transient transfer                           |

| Control address space         | 64 bytes                                                                    |

| CPU interface                 | 8-bit I/F Z80, 6809 etc.                                                    |

| CFOIntenace                   | 16-bit I/F 8086, H8, 68000 etc.                                             |

| Message communication mode    |                                                                             |

| Communication sentence length | 1 to 128 words/frame (1 word = 16 bits)                                     |

| Data buffer size              | 128 words                                                                   |

|                               | (1 word: reserved for the system, 127 words: Message data)                  |

| Data communication time       | When communicating 128 words: 169.3 µs                                      |

| Data transfer system          | Status: Cyclic transfer                                                     |

|                               | Data communication: Transient transfer                                      |

| CPU interface                 | 8-bit I/F Z80, 6809 etc.                                                    |

|                               | 16-bit I/F 8086, H8, 68000 etc.                                             |

| Others                        |                                                                             |

| Package                       | 80 pin QFP (mold size: 12 x 12 x 1.4 mm)                                    |

| Power supply                  | 3.3 V±10%                                                                   |

| Storage temperature range     | -65 to +150°C                                                               |

| Operating temperature range   | -40 to +85°C                                                                |

#### 4. Hardware description

#### 4-1. A list of terminals (QFP-80)

| No. | Signal name | I/O | Logic    | Description                                           | 5V Interface |

|-----|-------------|-----|----------|-------------------------------------------------------|--------------|

| 4   | MOD         |     |          | Select operation mode (L: Message                     | Available    |

| 1   | MOD         | I   |          | communication, H: CPU emulation)                      | Available    |

| 2   | TUD         |     |          | Set operation when outputting watchdog                | Available    |

|     |             | I   |          | timer                                                 |              |

| 3   | TMD         | I   |          | Select watchdog timer                                 | Available    |

| 4   | LCK0        | Ι   |          | Division rate of local bus control clock<br>(LCLK): 0 | Available    |

| -   |             |     |          | Division rate of local bus control clock              | Ausilahla    |

| 5   | LCK1        | I   |          | (LCLK): 1                                             | Available    |

| 6   | LWT0        | I   | Positive | Interval time of local bus: 0                         | Available    |

| 7   | LWT1        | I   | Positive | Interval time of local bus: 1                         | Available    |

| 8   | LIF0        | I   |          | Local bus I/F mode 0                                  | Available    |

| 9   | LIF1        | I   |          | Local bus I/F mode 1                                  | Available    |

| 10  | VDD         | I   |          | +3.3 V power input                                    |              |

| 11  | #LCS        | I/O | Negative | Chip selection for local bus                          | Available    |

| 12  | #LWR        | I/O | Negative | Write signal for local bus                            | Available    |

| 13  | #LRD        | I/O | Negative | Read signal for local bus                             | Available    |

| 14  | LA0         | I/O | Positive | Address for local bus: 0                              | Available    |

| 15  | GND         | I   |          | GND                                                   |              |

| 16  | LA1         | I/O | Positive | Address for local bus: 1                              | Available    |

| 17  | LA2         | I/O | Positive | Address for local bus: 2                              | Available    |

| 18  | LA3         | I/O | Positive | Address for local bus: 3                              | Available    |

| 19  | LA4         | I/O | Positive | Address for local bus: 4                              | Available    |

| 20  | LA5         | I/O | Positive | Address for local bus: 5                              | Available    |

| 21  | VDD         |     |          | +3.3 V power input                                    |              |

| 22  | LD0         | В   | Positive | Data for local bus: 0                                 | Available    |

| 23  | LD1         | В   | Positive | Data for local bus: 1                                 | Available    |

| 24  | LD2         | В   | Positive | Data for local bus: 2                                 | Available    |

| 25  | LD3         | В   | Positive | Data for local bus: 3                                 | Available    |

| 26  | GND         | I   |          | GND                                                   |              |

| 27  | LD4         | В   | Positive | Data for local bus: 4                                 | Available    |

| 28  | LD5         | В   | Positive | Data for local bus: 5                                 | Available    |

| 29  | LD6         | В   | Positive | Data for local bus: 6                                 | Available    |

| 30  | LD7         | В   | Positive | Data for local bus: 7                                 | Available    |

| 31  | VDD         | I   |          | +3.3 V power input                                    |              |

| 32  | LD8         | В   | Positive | Data for local bus: 8                                 | Available    |

| 33  | LD9         | В   | Positive | Data for local bus: 9                                 | Available    |

| 34  | LD10        | В   | Positive | Data for local bus: 10                                | Available    |

| 35  | LD11        | B   | Positive | Data for local bus: 11                                | Available    |

| 36  | GND         | 1   |          | +GND                                                  |              |

| 37  | LD12        | B   | Positive | Data for local bus: 12                                | Available    |

| 38  | LD13        | B   | Positive | Data for local bus: 13                                | Available    |

| 39  | LD14        | B   | Positive | Data for local bus: 14                                | Available    |

| 40  | LD15        | B   | Positive | Data for local bus: 15                                | Available    |

| 41  | VDD         | 1   |          | +3.3 V power input                                    |              |

| 42  | #LWRQ       | O/I | Negative | Wait request for local bus                            | Available    |

| 43  | #LIRQ       | 0/I | Negative | Interrupt request for local bus                       | Available    |

| 44  | #LIFB       | 0   | Negative | Busy interface for local bus                          | Available    |

| 45  | #LRST       | 0   | Negative | Reset for local bus                                   | Available    |

| 46  | GND         | Ĭ   |          | GND                                                   |              |

| 47  | LCLK        | 0   |          | Local bus control block                               |              |

|     |             |     |          | When a communication error is received, this          |              |

| 48  | #MRER       | 0   | Negative | signal becomes L level for a rated interval.          | Available    |

| No.      | Signal name | I/O      | Logic                                       | Description                                    | 5V Interface |

|----------|-------------|----------|---------------------------------------------|------------------------------------------------|--------------|

| 49 #MSEL | 0           | Negative | When sending data to this chip, this signal | Available                                      |              |

| 49       | #IVISEL     | 0        | negative                                    | becomes L level for a rated interval.          | Available    |

| 50       | VDD         | I        |                                             | +3.3 V power input                             |              |

| 51       | SOEH        | 0        | Positive                                    | Enable serial output                           |              |

| 52       | #SOEL       | 0        | Negative                                    | Enable serial output                           |              |

| 53       | SO          | 0        | Positive                                    | Serial output                                  |              |

| 54       | #TOUT       | 0        | Negative                                    | Watchdog timer output                          | Available    |

| 55       | #DNSO       | 0        | Negative                                    | Serial output of device number for next chip   | Available    |

| 56       | GND         | I        |                                             | GND                                            |              |

| 57       | BRK         | I        | Positive                                    | Break frame send request                       | Available    |

| 58       | SPD0        | I        |                                             | Communication speed: 0                         | Available    |

| 59       | SPD1        | I        |                                             | Communication speed: 1                         | Available    |

| 60       | CKSL        | I        |                                             | Clock rate selection (L: 40 MHz, H: 80 MHz)    | Available    |

| 61       | DNSM        | I        |                                             | Device number selection mode                   | Available    |

| 62       | #DN0        | I        | Negative                                    | Device number bit 0 (common with serial input) | Available    |

| 63       | #DN1        | I        | Negative                                    | Device number bit 1                            | Available    |

| 64       | #DN2        | I        | Negative                                    | Device number bit 2                            | Available    |

| 65       | #DN3        | I        | Negative                                    | Device number bit 3                            | Available    |

| 66       | #DN4        | I        | Negative                                    | Device number bit 4                            | Available    |

| 67       | #DN5        | I        | Negative                                    | Device number bit 5                            | Available    |

| 68       | VDD         | I        |                                             | +3.3 V power input                             |              |

| 69       | SI          | I        | Positive                                    | Serial input                                   |              |

| 70       | SOEI        | I        | Positive                                    | Enable serial output                           |              |

| 71       | GND         | I        |                                             | GND                                            |              |

| 72       | CLK         | I        |                                             | Reference clock                                |              |

| 73       | VDD         | I        |                                             | +3.3 V power input                             |              |

| 74       | #RST        | I        | Negative                                    | Reset                                          |              |

| 75       | GND         | I        | -                                           | GND                                            |              |

| 76       | GND         | I        |                                             | GND                                            |              |

| 77       | VDD         | I        |                                             | +3.3 V power input                             |              |

| 78       | GND         | I        |                                             | GND                                            |              |

| 79       | GND         | I        |                                             | GND                                            |              |

| 80       | GND         | I        |                                             | GND                                            |              |

Note 1: In the "I/O" column, each pin can be set for input or output using the operation mode (MOD). In the "I/O" column, "I" refers to input, "O" refers to output and "B" refers to bi-directional.

Note 2: As for the terminals with "available" in the 5V interface column, note the following. \* These terminals can be input 5 V level signals. These are the input that diode overcurrent protection is deleted on 3.3 V lines. If over voltage may possibly be charged due to reflection, linking, or inductive noise, we recommend inserting a diode for overcurrent protection.

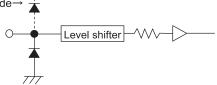

Without overcurrent protection diode  $\rightarrow$

- \* Outputs (including bi-directional) from 5V devices can be connected to the center device as far as these are TTL level. (Even when a signal is pulled up to 5V, the output level will be less than 3.3 V.) However, CMOS level signals cannot be connected.

- \* On the CPU bus interface, pull up of a 5 V level is possible for stabilizing bus lines (prevent floating). Use 10 k-ohm or larger capacity pull up resistors.

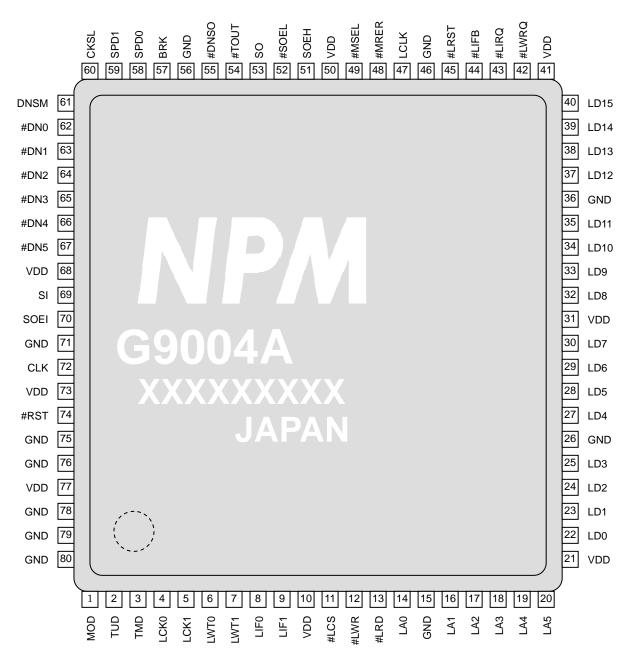

#### 4-2. Terminal assignment drawings

Note: Locate each pin number from the markings on the chip.

As shown in the figure above, pin number 1 is at the lower left of the NPM logo mark.

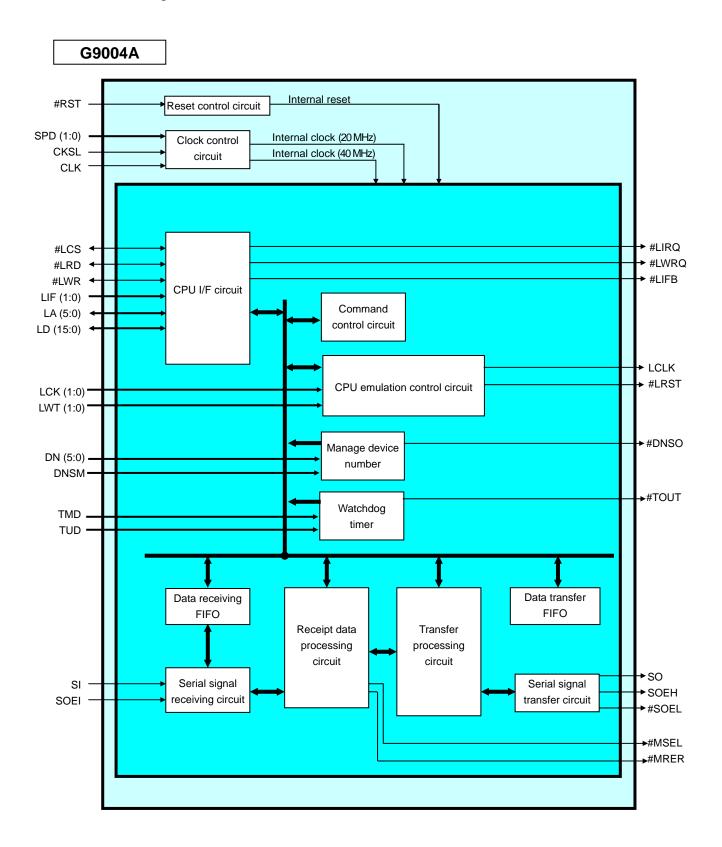

#### 4-3. Entire block diagram

#### 5. Functions of terminals

#### 5-1. CLK

This is an input terminal of the reference clock. By setting of the CKSL terminal, either of the following clock rate signals can be connected.

CKSL = L: 40 MHz CKSL = H: 80 MHz

By selecting either of these clock rates, the serial communication transfer rate does not change. This clock rate selection affects communication precision.

For a small-scale serial communication and transfer rate below 10 Mbps, use of the center device with 40 MHz does not give any restriction.

With 20 Mbps transfer speed; however, longer communication lines or a large number of connected local devices may deteriorate communication precision due to collapse of signals on the circuit. This deterioration of communication quality can be corrected inside the LSI, if the deterioration level is not much. In order to improve correction precision; however, evenness of the clock duty is required. In other words, if the duty is ideal (50:50), the capacity to correct collapse of the signals in the communication lines can be improved. On the contrary, if the duty is not ideal, the center device cannot cope with collapses of the communication line.

As a result, if the duty is close to ideal, the center device can be used with 40 MHz. When connecting more than one oscillator, the duty will not be ideal. In this case, select 80 MHz. The center device divides the frequency inside and creates 40 MHz frequency.

If you do not want to 80 MHz frequency, you may prepare a separate 40 MHz oscillator for this LSI.

#### 5-2. #RST

This is an input terminal for a reset signal.

By inputting an L level signal, the center device is reset.

The RST line must be held LOW for at least 12 reference clock cycles.

After turning ON the power, a reset signal must be input before starting communication.

#### 5-3. #DN0 to 5

Input terminals for setting device address.

Since these terminals use negative logic, setting all the terminals to zero calls up device address "3FH." There are two methods for entering a device address. Select the input method using the DNSM terminal.

#### 5-4. DNSM

Select the input method for loading the device address.

1) When the DNSM = H

Input numeric values 0 to 3Fh with negative logic using DIP-SW etc. for #DN0 to #DN5 terminals.

2) When the DNSM = L

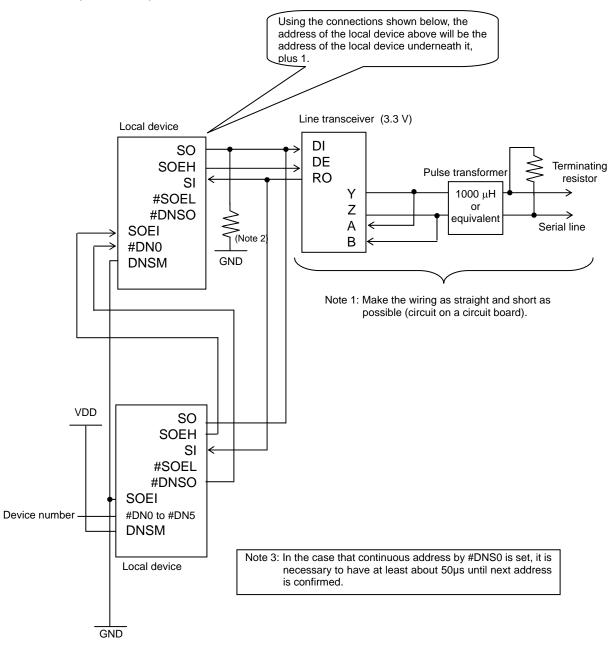

Input a #DNSO signal that is output by some other chip on the #DN0 terminal on this device. When using this input method, this chip has an address equal to the other chip's address plus one. When using this method, connect terminals #DN1 to #DN5 to GND.

When two sequential sets of serial data match, the data is taken to be a device address.

#### 5-5. #DNSO

The numeric equivalent of the address on #DN0 to #DN5 + 1 will be output after being converted into a serial bit stream.

Connect this output to another local device's #DN0 terminal (make all the other DNSM terminals of that local device LOW), so that other devices can get the address and pass it along to the next data-sending device.

In the case that continuous address by #DNSO signal is set, it is necessary to have at least about 50  $\mu$ s until the next step address is confirmed.

#### 5-6. SPD0, SPD1

Specify communication speed with these terminals.

All of the devices on the communication line shall be set to the same speed.

| SPD1 | SPD0 | Communication speed |

|------|------|---------------------|

| L    | L    | 2.5 Mbps            |

| L    | Н    | 5 Mbps              |

| Н    | L    | 10 Mbps             |

| Н    | Н    | 20 Mbps             |

#### 5-7. TUD

A watchdog timer is included on the chip to assist in administration of the communication status. When the data transmission interval from a center device to this device exceeds the set time, the watchdog timer times out.

This terminal is used to set output conditions when the watchdog timer times out.

When TUD = HIGH --- The LSI keeps its current status.

When the TUD = LOW --- The LSI is Reset.

#### 5-8. TMD

Specify the time for the watchdog timer.

The watchdog timer is used to administer the communication status.

When the interval between data packets sent from a center device is longer than the specified interval, the watchdog timer times out (the timer restarts its count at the end of each data packet received from a center device). The time out may occur because of a problem on the communication circuit, such as disconnection, or simply because the center device has stopped communicating. The time used by the watchdog timer varies with communication speed selected.

| TMD torminal |         | Watchdog ti | mer setting |          |

|--------------|---------|-------------|-------------|----------|

| TMD terminal | 20 Mbps | 10 Mbps     | 5 Mbps      | 2.5 Mbps |

| L            | 5 ms    | 10 ms       | 20 ms       | 40 ms    |

| Н            | 20 ms   | 40 ms       | 80 ms       | 160 ms   |

#### 5-9. #TOUT

Once the watchdog timer has timed out, this terminal goes LOW.

#### 5-10. SO

Serial output signal for communication. (Positive logic, tri-state output)

#### 5-11. SOEH, #SOEL

Output enable signal for communication. Difference between SOEH and #SOEL is that only the logic is different. When sending signals, SOEH will become H and #SOEL will become L.

#### 5-12. SOEI

When using more than one device (G9004A), connect the SOEH signal of the other device (G9004A) to this terminal.

By being wire OR'ed with the output enable signal from this I/O device, the device outputs an enable signal to SOEH or SOEL.

When not used, connect to the GND.

#### 5-13. SI

Serial input signal for communication. (Positive logic)

#### 5-14. #MRER

This is a monitor output to check communication quality.

When the center device receives an error frame such as a CRC error, the signal becomes L only for 128 cycles (3.2  $\mu$ s) of the CLK.

By measuring the condition using the counter, you can check communication quality.

#### 5-15. #MSEL

Communication status monitor output.

When this device receives a frame intended for this device and everything is normal (when communication #MRER is OFF), this terminal goes LOW for exactly 128 CLK cycles (3.2  $\mu$ s). This can be used to check the cyclic communication time.

#### 5-16. BRK

By providing HIGH pulses that are longer than the specified interval, this device will be made to wait for a break frame.

When this device receives a break frame send request from a center device, it immediately sends a break frame.

A pulse at least 3200 µsec long is needed, in order to be seen as the BRK input pulse (positive logic).

#### 5-17. MOD

Selects the operating mode for this IC. MOD = L: Message communication mode MOD= H: CPU emulation mode

#### 5-18. LCK0 to 1

Selects the clock frequency (LCLK) for controlling a local bus.

| LCK1 | LCK 0 | The clock frequency (LCLK) |

|------|-------|----------------------------|

| L    | L     | 2 MHz                      |

| L    | Н     | 4 MHz                      |

| Н    | L     | 10 MHz                     |

| Н    | Н     | 20 MHz                     |

When this IC is in CPU emulation mode, the speed of the emulation depends on the above setting. However, when the message communication mode is selected, only the LCLK output frequency will change, and the operation speed remains constant.

#### 5-19. LCLK

Outputs a clock for controlling a local bus. If needed, it can be used for an external circuit.

#### 5-20. LIF0 to 1

Using these terminals, select the CPU interface specifications for the local bus.

| LĬF1 | LIF 0 | CPU-I/F interface              |

|------|-------|--------------------------------|

| L    | L     | I/F-16 bit (2) (68000, etc)    |

| L    | Н     | I/F-16 bit (1) (8086, H8, etc) |

| Н    | L     | I/F-8 bit (2) (6809, etc)      |

| Н    | Н     | I/F-8 bit (1) (Z80, etc)       |

#### 5-21. #LRST

Output a reset signal for the local bus.

In any of the following cases, this signal goes LOW.

1) When a LOW is applied to the #RST terminal.

2) When TUD is LOW, the watchdog timer has timed out (only effective during approximate 32 cycles on LCLK).

The #LRST terminal status can be changed by setting bit 1 of port 3 (See section 6 "Setting the status information and G9004A operation information.")

(When bit 1 = 0, #LRST = HIGH. When bit 1 = 1, #LRST = LOW.)

#### 5-22. #LIFB

Outputs an interface busy signal for the local bus.

Use this signal in the message communication mode when connecting to a CPU that does not have a wait control input terminal.

This terminal goes LOW when a command or data is sent from a CPU, or when the status is being read. When this LSI completes its internal processing, it goes HIGH. Make sure that this terminal is HIGH, and then you can access the LSI.

This terminal cannot be used in the CPU emulation mode.

#### 5-23. LA0 to LA5

Address signals for the local bus. These will be either input or output terminals, depending on the mode selected.

In the CPU emulation mode, the device outputs address signals from terminals LA0 to LA5. In the message communication mode, input address signals on LA0 and LA1. Pull LA2 to LA5 down to GND (5~10Kohm resistors).

#### 5-24. #LCS

This is a chip select signal for the local bus. It will be either an input or output terminal, depending on the mode selected.

In the CPU emulation mode, this device outputs a chip select signal for an external circuit. In the message communication mode, you supply a chip select signal that will be used to access this LSI.

#### 5-25. #LWR

This terminal is used for a write signal for a local bus. It will be either an input or output terminal, depending on the mode selected.

In the CPU emulation mode, this terminal outputs a write signal for external circuit.

In the message communication mode, you supply a write signal in order to access this LSI.

#### 5-26. #LRD

This terminal is used for a read signal for a local bus. It will be either an input or output terminal, depending on the mode selected.

In the CPU emulation mode, this terminal outputs a read signal for an external circuit.

In the message communication mode, you supply a read signal in order to access this LSI.

#### 5-27. #LWRQ

This terminal is used for a wait request signal for a local bus. It will be either an input or output terminal, depending on the mode selected.

In the CPU emulation mode, you supply a wait request signal from an external circuit.

In the message communication mode, this terminal outputs a wait request signal when the device cannot be accessed.

#### 5-28. #LIRQ

This terminal is used for an interrupt request signal for a local bus. It will be either an input or output terminal, depending on the mode selected.

In the CPU emulation mode, you supply an interrupt request signal from an external circuit. In the message communication mode, this terminal outputs an interrupt request signal from internal operations.

#### 5-29. LD0 to LD7

These terminals are used for the low-byte signals of a local data bus. These are bi-directional terminals.

#### 5-30. LD8 to LD15

These terminals are used for the high-byte signals of a local data bus. These are bi-directional terminals. When using an 8-bit CPU interface, pull up these terminals to VDD (5 to 10 K-ohm resistors).

#### 5-31. LWT0 and LWT1

These terminals are used to set the time interval between writing and reading to a local bus. Use these terminals only in the CPU emulation mode. These are not used in the message communication mode.

| (T <sub>LCLK</sub> : LCLK clock cycle) |  |

|----------------------------------------|--|

|----------------------------------------|--|

| LWT1 | LWT0 | Time interval       |

|------|------|---------------------|

| L    | L    | T <sub>LCLK</sub>   |

| L    | Н    | 3xT <sub>LCLK</sub> |

| Н    | L    | 5xT <sub>LCLK</sub> |

| Н    | Н    | 9xT <sub>LCLK</sub> |

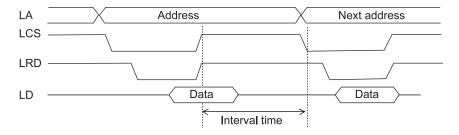

[An example of the reading procedure when using a 16-bit CPU interface (1)]

#### 5-32. CKSL

Selects the clock specifications for the input on the CLK terminal. When CKSL = L, supply a 40 MHz clock signal on the CLK terminal. The duty cycle should be approximately 50%.

If the duty cycle is too far away from 50%, the number of communication faults will increase. When CKSL = H, the device uses the CLK signal input after dividing by 2 internally. Therefore, the duty cycle will not have such a great influence. In this case, supply an 80 MHz clock signal.

#### 5-33. VDD, GND

Supply +3.3 VDC±10% for power on the VDD terminal. Make sure to use all the terminals.

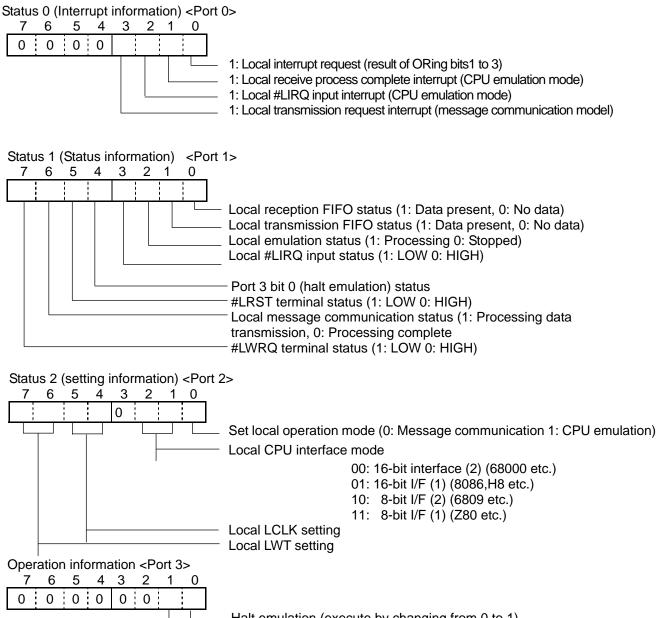

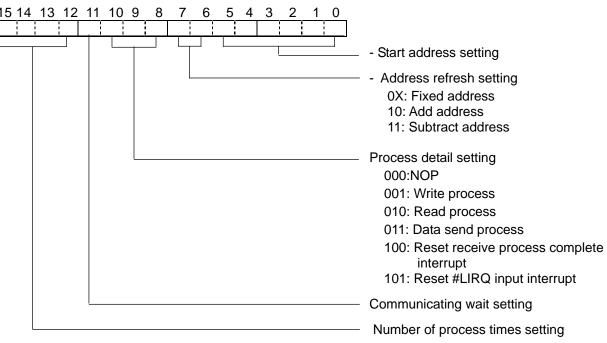

#### 6. Setting the status and operation information for the G9004A

During the cyclic communication and during data communication, the status register information (registers 0 to 2) is written to the port data area (ports 0 to 2) that corresponds to the device address in the center device. When the operating information is written to the port data area (port 3) that corresponds to the center device's device address, it is passed along to the CPU emulation device (G9004A) using the cyclic communication.

Halt emulation (execute by changing from 0 to 1) Change the #LRST terminal status (0: HIGH 1: LOW)

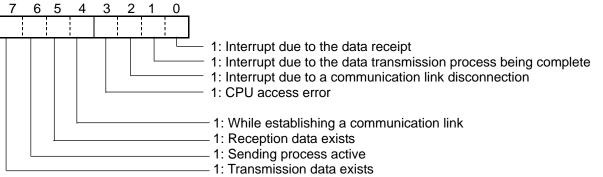

#### [Communication image]