## RemoteI/O & RemoteMotion

G9003 (PCL device)

# **User's Manual**

Nippon Pulse Motor Co., Ltd.

[Preface]

Thank you for considering our super high-speed serial communicator LSI, the "G9000." To learn how to use the G9000, read this manual to become familiar with the product. The handling precautions for installing this LSI are described at the end of this manual. Make sure to read them before installing the LSI.

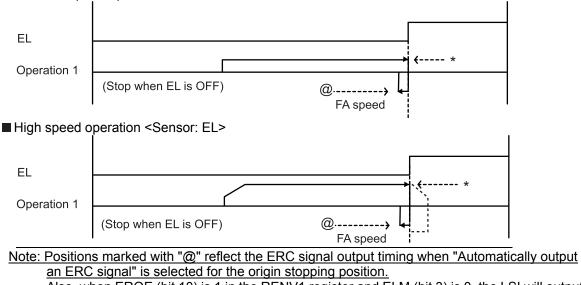

## [What the Motionnet is]

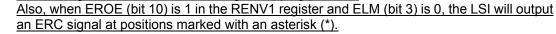

As a next generation communication system, the Motionnet can construct faster, more volume large scale, wire saving systems than conventional T-NET systems (conventional LSI product to construct serial communication system by NPM). Further, it has data communication function, which the T-NET does not have, so that the Motionnet can control data control devices such as in the PCL series (pulse train generation LSI made by NPM).

The Motionnet system consists of one center device connected to a CPU bus, and maximum 64 local devices, and they are connected by using cables of two or three conductive cores.

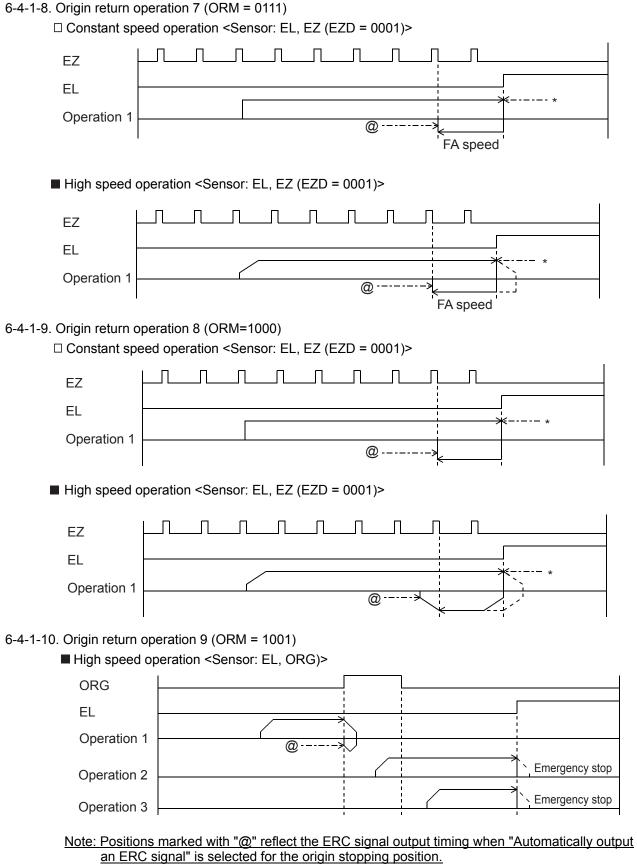

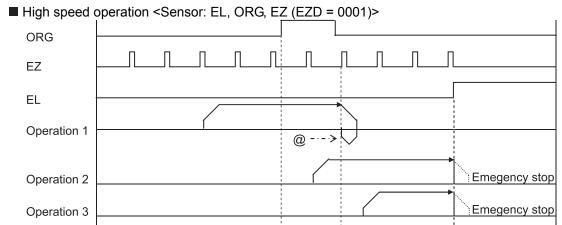

[Cautions]

(1) Copying all or any part of this manual without written approval is prohibited.

- (2) The specifications of this LSI may be changed to improve performance or quality without prior notice.

- (3) Although this manual was produced with the utmost care, if you find any points that are unclear, wrong, or have inadequate descriptions, please let us know.

(4) We are not responsible for any results that occur from using this LSI, regardless of item (3) above.

[Descriptions of indicators]

- (1) When describing register bits, "n" refers to the bit position and "0" refers to a bit position that can only be written with a "0." It also means the bit will always be read as "0"

- (2) Unless otherwise described, the timing for clocks discussed in this manual is a CLK speed of 40 MHz.

- (3) Terminal names and signal names that start with a # use negative logic. Ex.: #CS means that the CS terminal uses negative logic. This has the same meaning as  $\overline{cs}$ .

| INDEX |

|-------|

|-------|

| 1. | Outline                                          | 1  |

|----|--------------------------------------------------|----|

| 2. | Features                                         | 1  |

| 3. | Specifications                                   | 5  |

|    | 3-1. Device specifications                       | 5  |

|    | 3-2. Communication system specifications         |    |

|    | 3-3. Specifications for the axis control section |    |

|    |                                                  |    |

| 4. | Hardware description                             | 7  |

|    | 4-1. A list of terminals.                        | 7  |

|    | 4-2. Terminal allocation diagram                 |    |

|    | 4-3. Entire block diagram                        |    |

|    | 4-4. Functions of terminals                      |    |

|    | 4-4-1. CLK                                       |    |

|    | 4-4-2. #RST                                      |    |

|    | 4-4-3. CKSL                                      |    |

|    | 4-4-4. #DN0 to #DN5                              |    |

|    | 4-4-5. DNSM                                      |    |

|    | 4-4-6. #DNSO                                     |    |

|    | 4-4-7. SPD0, SPD1                                |    |

|    | 4-4-8. TUD                                       |    |

|    | 4-4-9. TMD                                       |    |

|    | 4-4-10. #TOUT                                    |    |

|    | 4-4-11. SO                                       |    |

|    | 4-4-12. SOEH, #SOEL                              |    |

|    | 4-4-13. SOEL.                                    |    |

|    | 4-4-14. SI                                       |    |

|    | 4-4-15. #MRER                                    |    |

|    | 4-4-15. #MRER                                    |    |

|    | 4-4-10. #MSEL                                    |    |

|    | 4-4-17. BRN                                      |    |

|    | 4-4-18. F0.10 F7                                 |    |

|    | 4-4-19. #STA, #STP                               |    |

|    | 4-4-20. #ENIG                                    |    |

|    | 4-4-21. ELL                                      |    |

|    | 4-4-22. +EL, -EL                                 |    |

|    | 4-4-25. SD                                       |    |

|    | 4-4-24. ORG                                      |    |

|    | 4-4-25. ALM                                      |    |

|    | 4-4-20. 001, DIR                                 |    |

|    | 4-4-27. FA, FB                                   |    |

|    |                                                  |    |

|    | 4-4-29. PCS                                      |    |

|    | 4-4-30. INP                                      |    |

|    | 4-4-31. CER                                      |    |

|    |                                                  |    |

|    | 4-4-33. ERC<br>4-4-34. #BSY/PH1                  |    |

|    |                                                  |    |

|    | 4-4-35. #FUP/PH2                                 |    |

|    | 4-4-36. #FDW/PH3                                 |    |

|    | 4-4-37. #MVC/PH4                                 |    |

|    | 4-4-38. #CP1                                     |    |

|    | 4-4-39. #CP2                                     |    |

|    | 4-4-40. #CP3                                     | 17 |

| 5. | Description of the software                                                                    |    |

|----|------------------------------------------------------------------------------------------------|----|

|    | 5-1. Outline of control                                                                        |    |

|    | 5-1-1. Communication control                                                                   |    |

|    | 5-1-2. Communication type                                                                      |    |

|    | 5-2. Functional settings for the PCL device (G9003)                                            | 20 |

|    | 5-2-1. I/O port                                                                                | 20 |

|    | 5-3. Commands (Operation commands & Control commands)                                          | 22 |

|    | 5-3-1. Operation commands                                                                      | 22 |

|    | 5-3-2. Control commands                                                                        |    |

|    | 5-3-3. Register control commands                                                               | 25 |

|    | 5-4. Register                                                                                  | 28 |

|    | 5-4-1. Speed setting registers                                                                 |    |

|    | 5-4-2. Environment settiong registers                                                          | 31 |

|    |                                                                                                |    |

| 6. | Operation mode                                                                                 |    |

|    | 6-1. Continuous operation mode using command control                                           | 50 |

|    | 6-2. Positioning operation mode                                                                |    |

|    | 6-2-1. Positioning operation (specify a target position using an incremental value) (MOD: 41h) |    |

|    | 6-2-2. Positioning operation (specify the absolute position in COUNTER1) (MOD: 42h)            |    |

|    | 6-2-3. Positioning operation (specify the absolute position in COUNTER2) (MOD: 43h)            |    |

|    | 6-2-4. Command position 0 return operation (MOD: 44h)                                          |    |

|    | 6-2-5. Machine position 0 return operation (MOD: 45h)                                          |    |

|    | 6-2-6. One pulse operation (MOD: 46h, 4Eh)                                                     |    |

|    | 6-2-7. Timer operation (MOD: 47h)                                                              | 51 |

|    | 6-3. Pulsar (PA/PB) input mode                                                                 | 52 |

|    | 6-3-1. Continuous operation using a pulsar input (MOD: 01h)                                    |    |

|    | 6-3-2. Positioning operation using a pulsar input (MOD: 51h)                                   | 55 |

|    | 6-3-3. Positioning operation using a pulsar input (specify the absolute position in COUNTER1)  |    |

|    | (MOD: 52h)                                                                                     | 55 |

|    | 6-3-4. Positioning operation using a pulsar input (specify the absolute position in COUNTER2)  |    |

|    | (MOD: 53h)                                                                                     |    |

|    | 6-3-5. Command position zero return operation using a pulsar input (MOD: 54h)                  |    |

|    | 6-3-6. Mechanical position zero return operation using a pulsar input (MOD: 54h)               |    |

|    | 6-4. Origin position operation mode                                                            |    |

|    | 6-4-1. Origin return operation                                                                 |    |

|    | 6-4-2. Leaving the origin position operations                                                  |    |

|    | 6-4-3. Origin search operation                                                                 | 66 |

|    | 6-5. EL or SL operation mode                                                                   |    |

|    | 6-5-1. Feed until reaching an EL or SL position                                                | 68 |

|    | 6-5-2. Leaving an EL or SL position                                                            | 68 |

|    | 6-6. EZ count operation mode                                                                   | 68 |

|    |                                                                                                |    |

| 7. | Speed patterns                                                                                 |    |

|    | 7-1. Speed patterns                                                                            |    |

|    | 7-2. Speed pattern settings                                                                    |    |

|    | 7-3. Manual FH correction                                                                      |    |

|    | 7-4. Example of setting up an acceleration/deceleration speed pattern                          |    |

|    | 7-5. Changing speed patterns while in operation                                                | 80 |

| _  |                                                                                                | -  |

| 8. | Description of the functions                                                                   |    |

|    | 8-1. Reset                                                                                     |    |

|    | 8-2. Position override                                                                         |    |

|    | 8-2-1. Target position override 1                                                              | 81 |

|    | 8-2-2. Target position override 2 (PCS signal)                                                 |    |

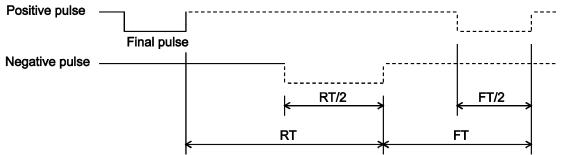

|    | 8-3. Output pulse control                                                                      |    |

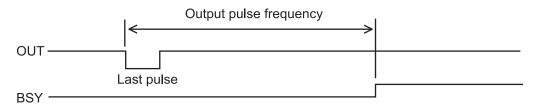

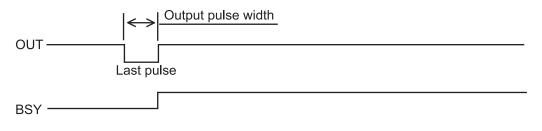

|    | 8-3-1. Output pulse mode                                                                       | 83 |

|    | 8-3-2. Control the output pulse width and operation complete timing                            |    |

|    | 8-4. Idling control                                                                            | 85 |

|    | 8-5. Mechanical external input control                                                                                                | 86  |

|----|---------------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 8-5-1. +EL, -EL signal.                                                                                                               | 86  |

|    | 8-5-2. SD signal                                                                                                                      | 86  |

|    | 8-5-3. ORG, EZ signal                                                                                                                 |     |

|    | 8-6. Servomotor I/F (Case in digital servo)                                                                                           | 90  |

|    | 8-6-1. INP signal                                                                                                                     |     |

|    | 8-6-2. ERC signal                                                                                                                     |     |

|    | 8-6-3. ALM signal                                                                                                                     |     |

|    | 8-7. External start, simultaneous start                                                                                               |     |

|    | 8-8. External stop / simultaneous stop.                                                                                               |     |

|    | 8-9. Emergency stop.                                                                                                                  |     |

|    | 8-10. Counter                                                                                                                         |     |

|    | 8-10-1. Counter type and input method                                                                                                 |     |

|    | 8-10-2. Counter reset                                                                                                                 |     |

|    | 8-10-3. Latch the counter and count condition                                                                                         |     |

|    | 8-10-4. Stop the counter and count condition                                                                                          |     |

|    | 8-11. Comparator                                                                                                                      |     |

|    | 8-11-1. Comparator types and functions                                                                                                |     |

|    | 8-11-2. Software limit function                                                                                                       |     |

|    | 8-11-2. Software limit function                                                                                                       | 105 |

|    |                                                                                                                                       |     |

|    | 8-11-4. IDX (synchronous) signal output function                                                                                      |     |

|    | 8-13. Vibration restriction function                                                                                                  |     |

|    | 8-14. Excitation sequence for stepper motors                                                                                          |     |

|    |                                                                                                                                       |     |

|    | 8-15. General-purpose I/O terminals (P0 to P7)<br>8-16. Interrupt output                                                              |     |

|    | 0-10. Interrupt output                                                                                                                | 114 |

| 0  | How to calculate the communication cycle time                                                                                         | 117 |

| 9. | 9-1. Time required for one cycle                                                                                                      | 117 |

|    |                                                                                                                                       |     |

|    | <ul><li>9-2. Time required for one complete data communication</li><li>9-3. Total cycle time (including data communication)</li></ul> |     |

|    |                                                                                                                                       | 117 |

| 10 | . Electrical characteristics                                                                                                          | 110 |

| 10 | 10-1. Absolute maximum ratings                                                                                                        |     |

|    | 10-2. Recommended operating conditions                                                                                                | 110 |

|    | 10-3. DC characterstics                                                                                                               |     |

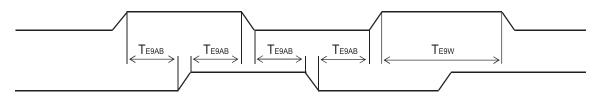

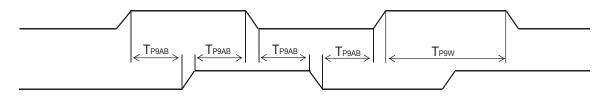

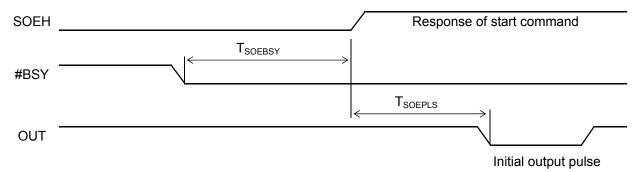

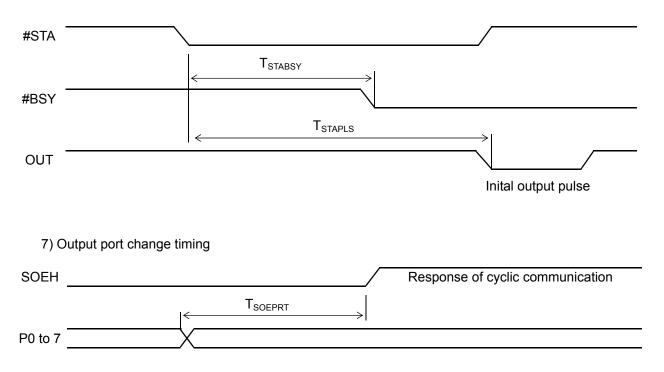

|    | 10-4. AC characteristics                                                                                                              |     |

|    | 10-4-1. System clock                                                                                                                  |     |

|    | 10-4-1. System clock                                                                                                                  |     |

|    |                                                                                                                                       |     |

|    | 10-5. Operation timing                                                                                                                | 120 |

| 11 | Comunication overhele                                                                                                                 | 100 |

| 11 | Comunication example                                                                                                                  |     |

|    |                                                                                                                                       |     |

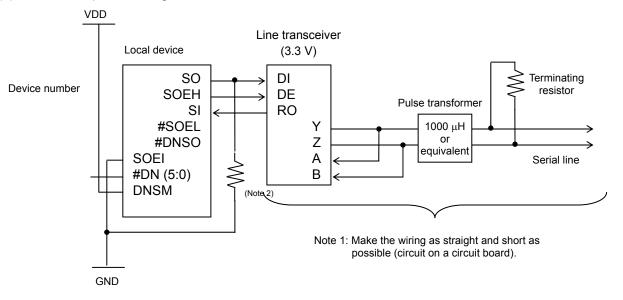

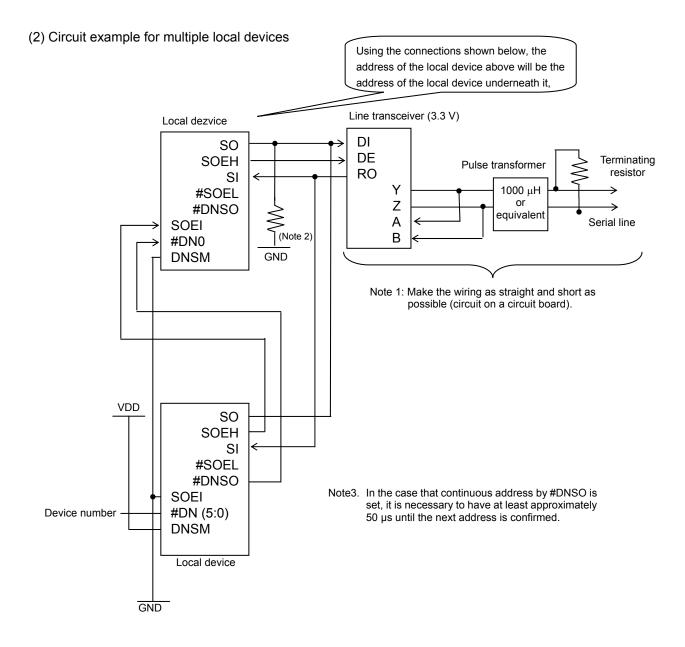

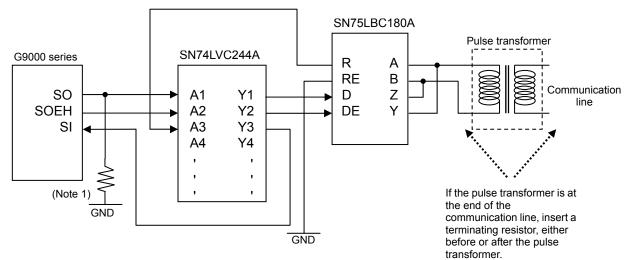

|    | 11-2. A connection example of a level shifter                                                                                         |     |

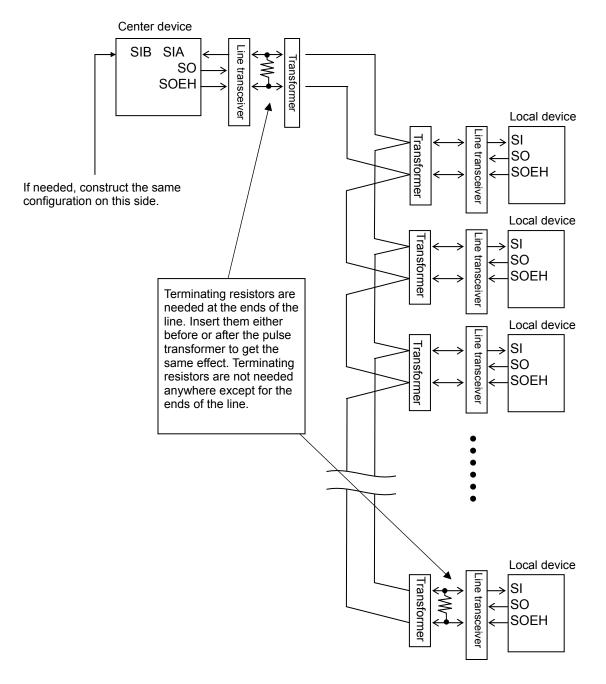

|    | 11-3. Complete configuration                                                                                                          | 126 |

| 40 | De service de de service en t                                                                                                         | 407 |

| 12 | . Recommended environment                                                                                                             |     |

|    | 12-1. Cable                                                                                                                           |     |

|    | 12-2. Terminating resistor                                                                                                            |     |

|    | 12-3. Pulse transformer                                                                                                               |     |

|    | 12-4. I/F chip                                                                                                                        |     |

|    | 12-5. Parts used in our experiments                                                                                                   |     |

|    | 12-6. Other precautions                                                                                                               | 128 |

|    |                                                                                                                                       | 400 |

| 13 | . Software example                                                                                                                    |     |

|    | 13-1. Environment and precautions used for descriptions                                                                               |     |

|    | 13-2. Command used                                                                                                                    |     |

|    | 13-3. Center device address map                                                                                                       |     |

|    | 13-4. Center device status                                                                                                            | 131 |

| 13-5. Interrupt status                                                              | 132 |

|-------------------------------------------------------------------------------------|-----|

| 13-6. Center device command                                                         | 133 |

| 13-7. Start of the simplest cyclic communication                                    |     |

| 13-8. Communication with port data (port data and data device status)               |     |

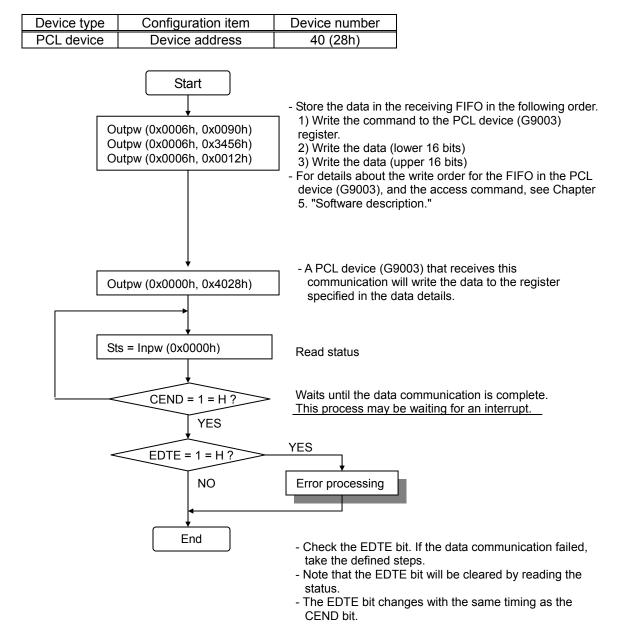

| 13-9. Data communication 1: Put the value in the register of the PCL device (G9003) |     |

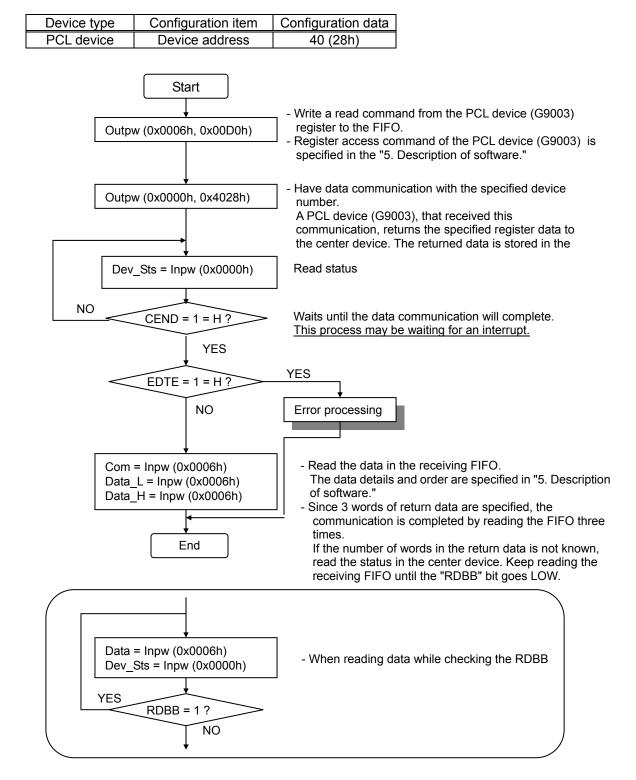

| 13-10. Data communication 2: Read a register in a PCL device (G9003)                |     |

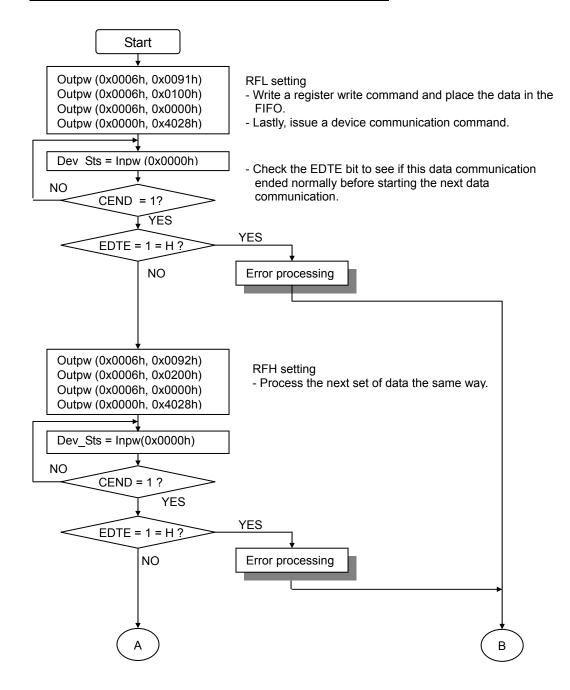

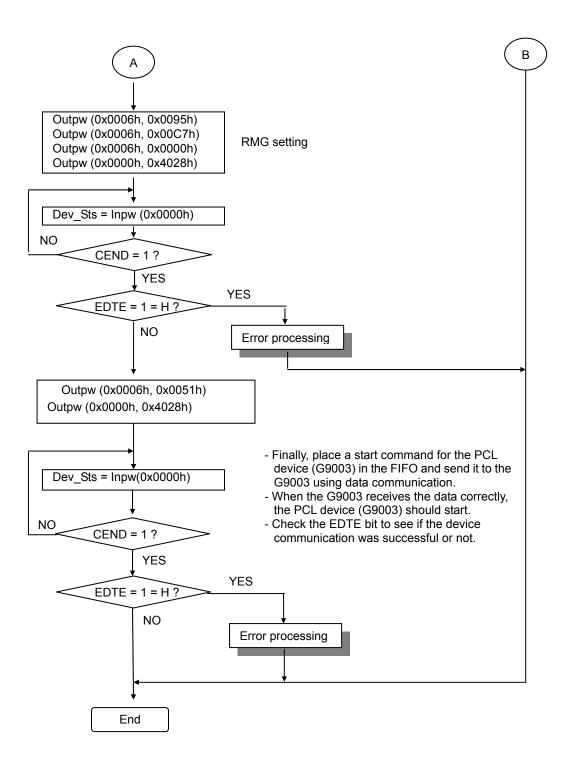

| 13-11. Data communication 3: Start the PCL device (G9003).                          |     |

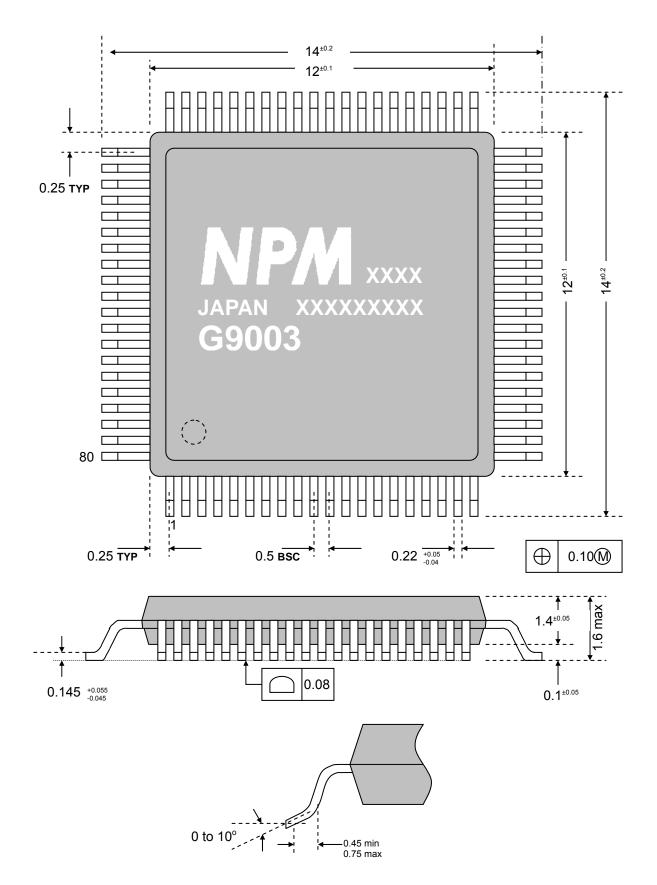

| 14. External dimensions                                                             | 142 |

| Handling Precautions                                                                | 143 |

| 1. Design precautions                                                               | 143 |

| 2. Precautions for transporting and storing LSIs                                    | 143 |

| 3. Precautions for mounting                                                         | 143 |

| 4. Other precautions                                                                |     |

| •                                                                                   |     |

## 1. Outline

This LSI is an axis control device for the Motionnet system. On receiving a command from the center device (G9001A), it can output high-speed pulses to drive stepper motors and servomotors.

Using a variety of speed patterns, including constant speed, linear acceleration/deceleration, and S-curve acceleration/deceleration, this device affords control of various actions including continuous feeding, positioning, and origin return operations.

If all of the devices connected to a center device are PCL devices (G9003), the system can be constructed to control up to 64 axes while reducing the needed wiring. Using routine communications, the system allows you to check the operation status and interrupt it with various conditions.

### 2. Features

- Communications

Maximum transfer speed is 20 Mbps.

The system can control up to 64 axes.

If a communication error occurs, it can stop outputting pulses and reset the output ports.

- Power supply

Single power supply voltage: +3.3 V. Interfaces with 5V ICs are possible (except for clock input and communication related terminals).

- Interrupt signal output

An interrupt request can be output to the center device by various factors.

- Acceleration/Deceleration speed control

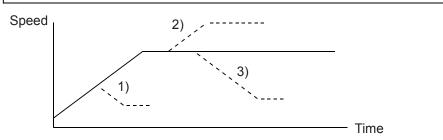

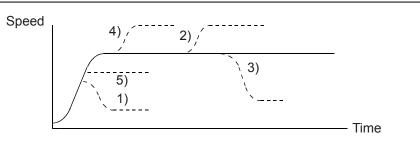

Linear acceleration/deceleration and S-curve acceleration/deceleration are available. Linear acceleration/deceleration can be inserted in the middle of an S-curve acceleration/deceleration curve. (Specify the S-curve range.)

The S-curve range can specify each acceleration and deceleration independently. Therefore, you can create an acceleration/deceleration profile that consists of linear acceleration and S-curve deceleration, or vice versa.

- Speed override

The feed speed can be changed in the middle of any feed operation.

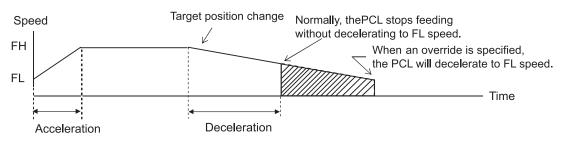

- Overriding target position 1) and 2)

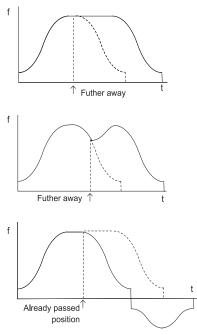

- The target position (feed amount) can be changed while feeding in the positioning mode. If the current position exceeds the newly entered position, the motor will decelerate, stop (immediate stop when already feeding at a constant speed), and then feed in the reverse direction for positioning.

- 2) Starts operation the same as in the continuous mode and, when it receives an external signal, it will stop after outputting the specified number of pulses.

- Triangle drive elimination (FH correction function) In the positioning mode, when there are a small number of output pulses, this function automatically lowers the maximum speed and eliminates triangle driving.

- Simultaneous start function Multiple axes controlled by the same LSI can be started at the same time using an external signal.

- Simultaneous stop function Multiple axes controlled by the same LSI can be stopped at the same time using an external signal.

- Excitation sequence for 2-phase stepper motors

This device can output excitation sequences for 2-phase stepper motors, for both unipolar and bipolar systems.

- A variety of counter circuits

The following four counters are available separately for each axis.

| Counter  | Use or purpose                                                                                                                                                                                    | Counter Input/Output                                                                                                                                                                  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| COUNTER1 | 28-bit counter for control of the command position                                                                                                                                                | Outputs pulses                                                                                                                                                                        |

| COUNTER2 | 28-bit counter for mechanical position control (Can be used as general-purpose counter)                                                                                                           | Outputs pulses<br>EA/EB input<br>PA/PB input                                                                                                                                          |

| COUNTER3 | 16-bit counter for controlling the deviation between<br>the command position and the machine's current<br>position, or 16-bit general-use counter with the<br>synchronous signal output function. | Outputs pulses<br>EA/EB input<br>PA/PB input<br>1/4096 of reference clock<br>Outputs pulses and EA/EB<br>input<br>Outputs pulses and PA/PB<br>input<br>EA/EB input and PA/PB<br>input |

All counters can be reset by writing a command or by providing a CLR signal.

The counter data can also be latched by writing a command, or by providing an LTC or ORG signal. COUNTER3 counters can be used as a ring counter that repeats counting through a specified counting range by using IDX (synchronous) signal output function.

- Comparator

There are three comparator circuits for each axis. They can be used to compare target values and internal counter values.

The counter to compare can be selected from COUNTER1 (command position counter), COUNTER2 (mechanical position counter), COUNTER3 (deflection counter).

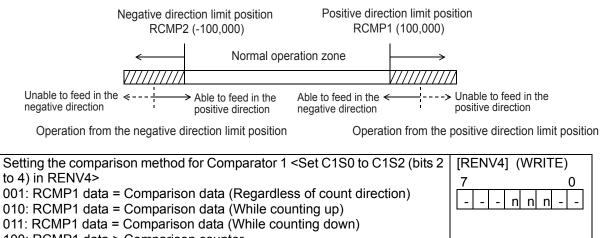

Comparators 1 and 2 can also be used as software limits (+SL, -SL).

- Software limit function

You can set software limits using 2 comparators' circuits.

When the mechanical position approaches the software limit range, the LSI will instruct the motors to stop immediately or to stop by deceleration. After that these axes can only be moved in the direction opposite their previous travel.

- Backlash correction function

The LSI has a backlash correction function.

Each time the feed direction is changed, the LSI applies a backlash correction

- Synchronous signal output function The LSI can output pulse signals at the specified intervals.

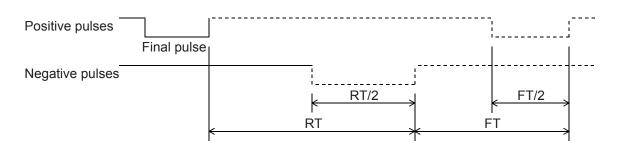

- Vibration restriction function

Specify a control constant in advance and add one pulse each for reverse and forward feed just before stopping.

Using this function, vibration can be decreased while stopping.

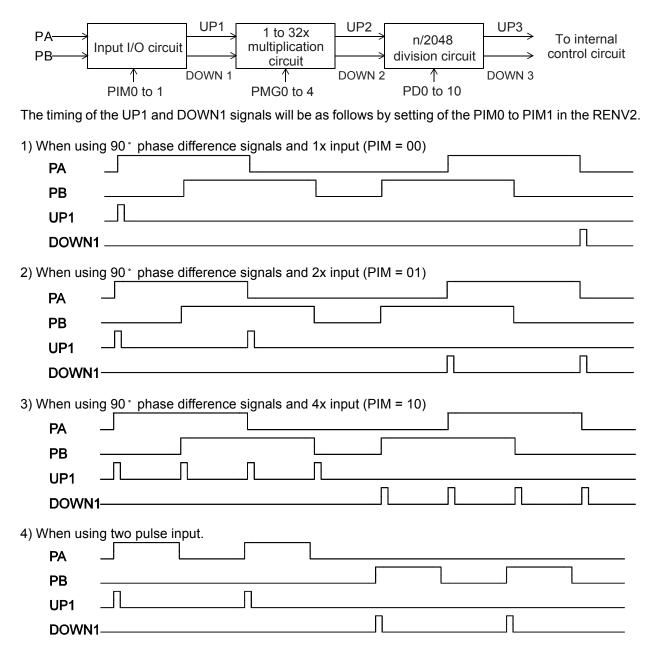

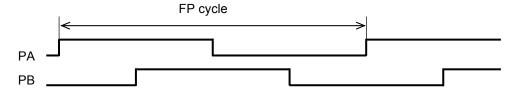

- Manual pulsar input function

By applying manual pulse signals (PA/PB), you can rotate a motor directly. The input signals can be 90 phase difference signals (1x, 2x, or 4x) or up and down signals. In addition to the magnification rates above, the LSI contains an integral pulse number magnification

circuit which multiplies by 1x to 32x and a pulse quantity division circuit which is divided by 2048 (1/2048 to 2048/2048).

EL signal and software limit settings can be used, and the LSI stops the output of pulses. It can also feed in the opposite direction.

- Out-of-step detection function

This LSI has a deflection counter which can be used to compare command pulses and encoder signals (EA/EB).

It can be used to detect out-of-step operations and to confirm a position by using a comparator.

- Output pulse specifications

Output pulses can be set to a Common pulse or Two-pulse mode. The output logic can also be selected.

- Idling pulse output function

This function outputs a preset number of pulses at the self-start frequency (FL) before a high-speed start acceleration operation.

Even if value near to the maximum starting pulse rate is set during the acceleration, this function is effective in preventing out-of-step operation for stepper motors.

- Operation mode

The basic operations of this LSI consists of continuous operation, positioning, and origin return. By setting the optional operation mode bits, you can use a variety of operations.

- <Examples of the operation modes>

- 1) Start/stop by command.

- 2) Continuous operation and positioning operation using PA/PB inputs (manual pulsar).

- 3) Origin return operation.

- 4) Positioning operation using commands.

- 5) Hardware start of the positioning operation using #STA input.

- 6) Change the target position after turning ON the PCS. (Delay control)

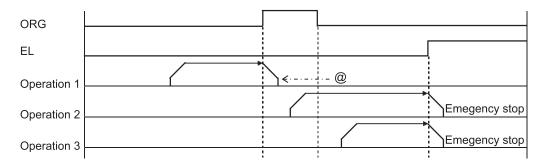

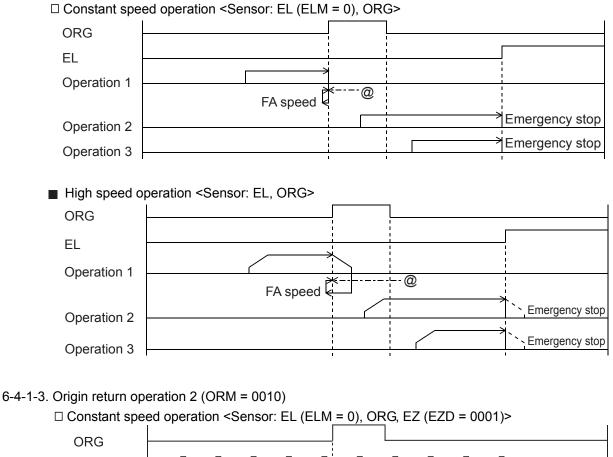

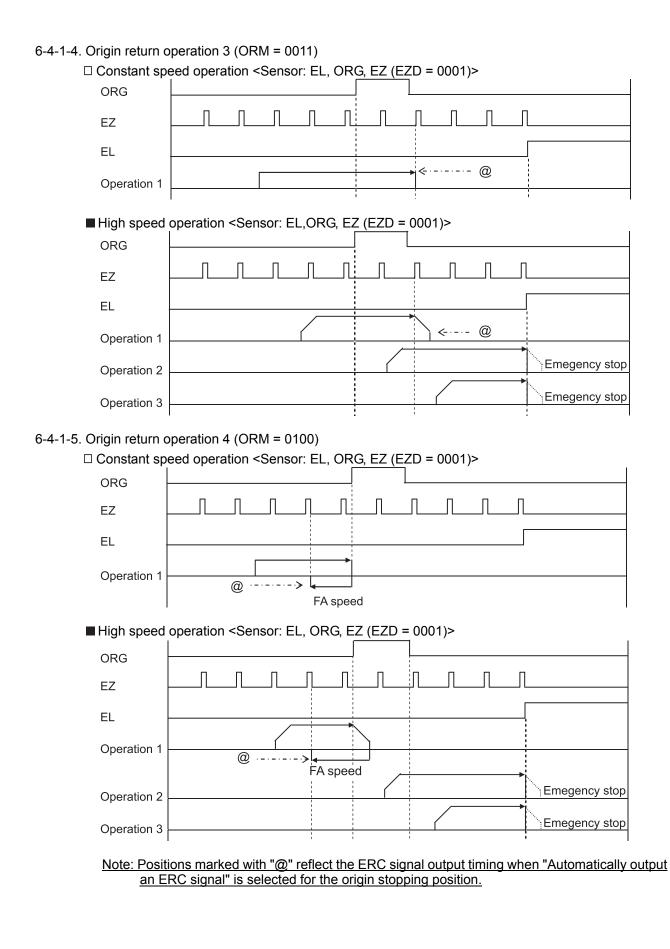

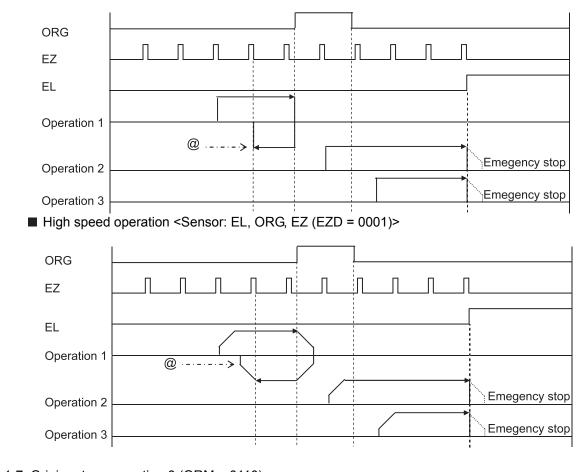

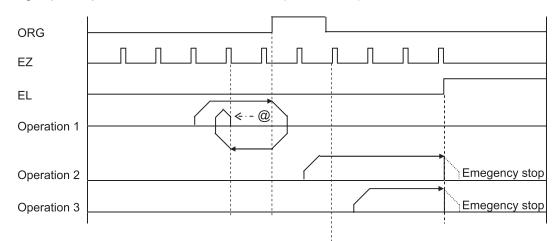

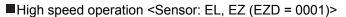

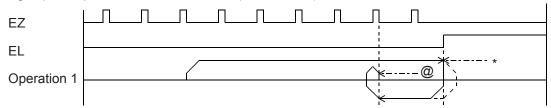

- Variety of origin return sequences

- 1) Feeds at constant speed and stops when the ORG signal is turned ON

- 2) Feeds at constant speed and stops when count up EZ signals.

- 3) Feeds at constant speed, reverses when the ORG signal is turned ON, and stops when an EZ signal is received.

- 4) Feeds at constant speed and stops when the EL signal is turned ON. (Normal stop)

- 5) Feeds at constant speed, reverses when the EL signal is turned ON, and stops when an EZ signal is received.

- 6) Feeds at high speed, decelerates when the SD signal is turned ON, and stops when the ORG signal is turned ON.

- 7) Feeds at high speed, decelerates when the ORG signal is turned ON, and stops when an EZ signal is received.

- 8) Feeds at high speed, decelerates and stops after the ORG signal is turned ON. Then, it reverse feeds and stops when an EZ signal is received.

- 9) Feeds at high speed, decelerates and stops by memorizing the position when the ORG signal is turned ON, and stops at the memorized position.

- 10) Feeds at high speed, decelerates to the position stored in memory when an EZ signal is received after the ORG signal is turned ON. Then, returns to the memorized position if an overrun occurs.

- 11) Feeds at high speed, reverses after a deceleration stop triggered by the EL signal, and stops when an EZ signal is received.

#### - Mechanical input signals

- The following four signals can be input.

- +EL: When this signal is turned ON, while feeding in the positive (+) direction, movement on this axis stops immediately (with deceleration). When this signal is ON, no further movement occurs on the axis in the positive (+) direction. (The motor can be rotated in the negative (-) direction.)

- 2) -EL: Functions the same as the +EL signal except that it works in the negative (-) direction.

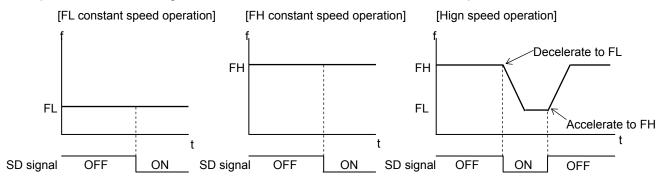

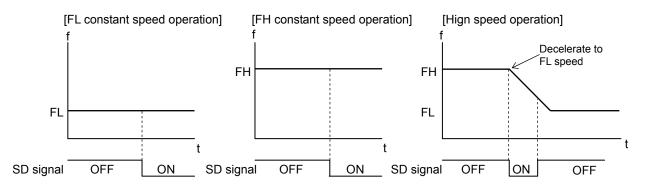

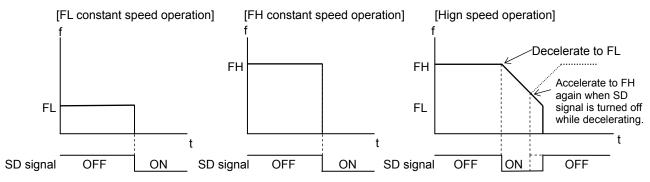

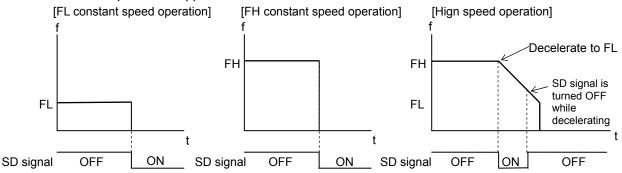

- 3) SD: This signal can be used as a deceleration signal or a deceleration stop signal, according to the software setting. When this is used as a deceleration signal, and when this signal is turned ON during a high speed feed operation, the motor on this axis will decelerate to the FL speed. If this signal is ON and movement on the axis is started, the motor on this axis will run at the FL constant speed. When this signal is used as a deceleration stop signal, and when this signal is turned ON during a high speed feed operation, the motor on this axis will decelerate to the FL speed. If this signal is used as a deceleration stop signal, and when this signal is turned ON during a high speed feed operation, the motor on this axis will decelerate to the FL speed and then stop.

- 4) ORG: Input signal for an origin return operation.

For safety, make sure the +EL and -EL signals stay on from the EL position until the end of each stroke. The input logic for these signals can be changed using the ELL terminal. The input logic of the SD and ORG signals can be changed using software.

- Digital servomotor I/F

- The following three signals can be used as an interface for each axis

- 1) INP: Input positioning complete signal that is output by a servomotor driver.

- 2) ERC: Output deflection counter clear signal to a servomotor driver.

- 3) ALM: Regardless of the direction of operation, when this signal is ON, movement on this axis stops immediately (deceleration stop). When this signal is ON, no movement can occur on this axis. The input logic of the INP, ERC, and ALM signals can be changed using software. The ERC signal is a pulsed output. The pulse length can be set. (12 µsec to 104 msec. A level output is also available.)

- Emergency stop signal (#EMG) input

When this signal is turned ON, movement on both axes stops immediately. While this signal is ON, no movement is allowed on any axes.

## 3. Specifications

3-1. Device specifications

| Item                         | Description                                                     |

|------------------------------|-----------------------------------------------------------------|

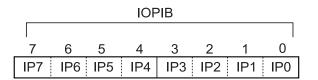

| General-purpose input/output | General-purpose input/output ports. (1 port = 8 bits)           |

|                              | Individual bits can be set for input or output.                 |

| Communication data length    | 1 to 4 words / frame (1 word = 16 bits)                         |

| Data buffer length           | 4 words                                                         |

| Data communication time      | When using 3-word communication (written to one register in the |

|                              | PCL device(G9003)) 19.3 µs                                      |

| Transfer system              | I/O ports: Cyclic transfer                                      |

| Transfer System              | Data communication: Transient transfer.                         |

| Package type                 | 80 pins QFP (Mold section: 12 x 12 x 1.4 mm)                    |

| Power supply                 | 3.3 V ±10%                                                      |

| Storage temperature range    | -40 to +125 C                                                   |

| Operating temperature range  | -40 to +85 C                                                    |

## 3-2. Communication system specifications

| Item                       | Description                  |

|----------------------------|------------------------------|

| Reference clock Note 1     | 40 MHz or 80 MHz             |

| Communication speed Note 2 | 2.5 M, 5 M, 10 M, or 20 Mbps |

| Communication sign         | NRZ sign                     |

| Communication protocol     | NPM original method          |

| Communication method       | Half-duplex communication    |

| Communication I/F Note 3   | RS-485 or pulse transformer  |

| Connection method          | Multi-drop connection        |

| Number of local devices    | 64 devices max.              |

Note 1: When to transfer data with 20 Mbps speed, and if the clock duty can be maintained to ideal "50:50" condition, the center device can be operated by inputting 40 MHz clock signal. The above ideal conditions mean that an oscillator and the PCL device (G9003) are connected as 1:1 and close to each other. Actually, even these good conditions cannot establish 50:50. However, a duty proximate to the ideal one will be established.

Even if the ideal duty is broken a little, when signal lines are shorter and/or the number of local devices is smaller, the center device can operate without any trouble. (For the details, see the section for the "CLK" terminal.)

When the signal lines are longer and/or the number of connected local devices is high and if it is difficult to warranty the clock duty, you should take measures such as to prepare an 80 MHz signal or a 40 MHz clock proprietary to the PCL device (G9003).

To select a clock rate, specify using the LSI terminal. In either clock rate, the maximum speed of 20 Mbps is the same.

- Note 2: Select the communication speed using the LSI terminal. Regardless of the selection of the communication speed, the input clock remains the same.

- Note 3: NPM recommends a system that uses a pulse transformer.

## 3-3. Specifications for the axis control section

| Item                                                               | Description                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Positioning control range                                          | -134,217,728 to +134,217,727 (28-bit)                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| setting range                                                      | 0 to 16,777,215 (24-bit)                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Number of registers used for setting speeds                        |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|                                                                    |                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| Speed magnification range                                          | Multiply by 0.1 to 66.6<br>Multiply by 0.1 = 0.1 to 10,000.0 pps<br>Multiply by 1 = 1 to 100,000 pps<br>Multiply by 50 = 50 to 5,000,000 pps                                                                                                                                                                                                         |  |  |  |  |

| Acceleration/deceleration characteristics                          | Selectable acceleration/deceleration pattern for both increasing and decreasing speed separately, using Linear and S-curve acceleration/deceleration.                                                                                                                                                                                                |  |  |  |  |

| Acceleration rate setting                                          | 1 to 65,535 (16-bit)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

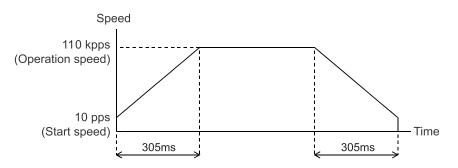

| range                                                              | Ex: $1 \rightarrow 100,000$ pps acceleration time: 80 msec (set 1) to 2621 sec (set 65535)                                                                                                                                                                                                                                                           |  |  |  |  |

| Deceleration rate setting range                                    | 1 to 65,535 (16-bit)                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| Ramping-down point automatic setting                               | Automatic setting within the range of (deceleration time) < (acceleration time x 2)                                                                                                                                                                                                                                                                  |  |  |  |  |

| FH correction function<br>(Eliminates triangle<br>pattern driving) | If the feed amount is too small, the PCL device (G9003) has to start decelerating before it has completed the acceleration, and this will create a triangular shaped speed pattern. In order to eliminate this triangular speed pattern, this function automatically reduces the operation speed so that the triangle speed pattern will be avoided. |  |  |  |  |

| Manual operation input                                             | Manual pulsar input                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Counter                                                            | COUNTER1: Command position counter (28-bit)<br>COUNTER2: Mechanical position counter (28-bit)<br>COUNTER3: Deflection counter (16-bit)                                                                                                                                                                                                               |  |  |  |  |

| Comparators                                                        | 28-bits x 3 circuits                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

Note 1: Values above 100,000 cannot be entered. Even if a value over 100,000 is entered, the register value will only be 100,000.

## 4. Hardware description

## 4-1. A list of terminals

| No. | Signal name | I/O            | Logic         | Description                                       | 5V interface |

|-----|-------------|----------------|---------------|---------------------------------------------------|--------------|

| 1   | VDD         |                |               | Power supply +3.3 V                               |              |

| 2   | #DN0        |                | Negativo      | Device number bit 0 (Common with the              | Possible     |

| 2   | #DNU        | Ι <sub>υ</sub> | Negative      | serial input)                                     | FUSSIBle     |

| 3   | #DN1        | Ι <sub>υ</sub> | Negative      | Device number bit 1                               | Possible     |

| 4   | #DN2        | Ι <sub>υ</sub> | Negative      | Device number bit 2                               | Possible     |

| 5   | #DN3        | Ι <sub>υ</sub> | Negative      | Device number bit 3                               | Possible     |

| 6   | #DN4        | lυ             | Negative      | Device number bit 4                               | Possible     |

| 7   | #DN5        | lυ             | Negative      | Device number bit 5                               | Possible     |

| 8   | VDD         |                |               | Power supply input +3.3 V                         |              |

| 9   | VDD         |                |               | Power supply input +3.3 V                         |              |

| 10  | VDD         |                |               | Power supply input +3.3 V                         |              |

| 11  | VDD         |                |               | Power supply input +3.3 V                         |              |

| 12  | GND         |                |               | GND                                               |              |

| 13  | #DNSO       | 0              | Negative      | Serial output of the next chips device<br>number  | Possible     |

| 14  | DNSM        | lυ             |               | Device number set mode                            | Possible     |

| 15  | SOEI        | I <sub>D</sub> | Positive      | Enable serial output                              |              |

| 16  | #SOEL       | Ő              | Negative      | Enable serial output                              |              |

| 17  | SOEH        | 0              | Positive      | Enable serial output                              |              |

| 18  | SO          | 0              | Positive      | Serial output                                     |              |

| 19  | GND         |                |               | GND                                               |              |

| 20  | SI          | I              | Positive      | Serial input                                      |              |

| 21  | GND         |                |               | GND                                               |              |

| 22  | VDD         |                |               | Power supply input +3.3V                          |              |

| 23  | VDD         |                |               | Power supply input +3.3V                          |              |

| 24  | EA          | lυ             |               | Encoder A phase signal                            | Possible     |

| 25  | EB          | lυ             |               | Encoder B phase signal                            | Possible     |

| 26  | EZ          | Ι <sub>υ</sub> | Negative<br>% | Encoder Z phase signal                            | Possible     |

| 27  | PA          | lυ             |               | Manual pulser A phase signal                      | Possible     |

| 28  | PB          | lυ             |               | Manual pulser B phase signal                      | Possible     |

| 29  | GND         |                |               | GND                                               |              |

| 30  | ERC         | 0              | Negative<br>% | Request to clear a deflection counter in a driver | Possible     |

| 31  | OUT         | 0              | Negative<br>% | Pulse train output                                | Possible     |

| 32  | DIR         | 0              |               | Feed direction                                    | Possible     |

| 33  | VDD         |                |               | Power supply input +3.3 V                         |              |

| 34  | #CP1        | 0              | Negative      | Comparator 1 output                               | Possible     |

| 35  | #CP2        | 0              | Negative      | Comparator 2 output                               | Possible     |

| 36  | #CP3        | 0              | Negative      | Comparator 3 output                               | Possible     |

| 37  | PCS         | Ι <sub>υ</sub> | Negative<br>% | Start positioning control                         | Possible     |

| 38  | LTC         | Ι <sub>υ</sub> | Negative<br>% | Counter value latch signal                        | Possible     |

| 39  | CLR         | Ιυ             | Negative<br>% | Counter clear signal                              | Possible     |

| 40  | INP         | Ι <sub>υ</sub> | Negative<br>% | In-position (Positioning complete)                | Possible     |

| 41  | GND         |                |               | GND                                               |              |

| 42  | #EMG        | Ι <sub>υ</sub> | Negative      | Emergency stop                                    | Possible     |

| 43  | +EL         | lυ             | Negative#     | (+) end limit                                     | Possible     |

| 44  | -EL         | Ι <sub>υ</sub> | Negative#     | (-) end limit                                     | Possible     |

| No. | Signal name | I/O            | Logic                 | Description                                                                             | 5V interface |

|-----|-------------|----------------|-----------------------|-----------------------------------------------------------------------------------------|--------------|

| 45  | SD          | Ιυ             | Negative<br>%         | Deceleration request signal                                                             | Possible     |

| 46  | ORG         | Ιυ             | Negative<br>%         | Origin position signal                                                                  | Possible     |

| 47  | ALM         | Ιυ             | Negative<br>%         | Alarm signal (Stop request)                                                             | Possible     |

| 48  | VDD         |                |                       | Power supply input +3.3 V                                                               |              |

| 49  | #STA        | Β <sub>υ</sub> | Negative              | External start                                                                          | Possible     |

| 50  | #STP        | Β <sub>υ</sub> | Negative              | External stop                                                                           | Possible     |

| 51  | P0          | Β <sub>υ</sub> |                       | General-purpose I/O terminal 0                                                          | Possible     |

| 52  | GND         |                |                       | GND                                                                                     |              |

| 53  | P1          | Bu             |                       | General-purpose I/O terminal 1                                                          | Possible     |

| 54  | P2          | Bu             |                       | General-purpose I/O terminal 2                                                          | Possible     |

| 55  | P3          | Bu             |                       | General-purpose I/O terminal 3                                                          | Possible     |

| 56  | P4          | Bu             |                       | General-purpose I/O terminal 4                                                          | Possible     |

| 57  | P5          | Bu             |                       | General-purpose I/O terminal 5                                                          | Possible     |

| 58  | P6          | Bu             |                       | General-purpose I/O terminal 6                                                          | Possible     |

| 59  | P7          | Bu             |                       | General-purpose I/O terminal 7                                                          | Possible     |

| 60  | VDD         | 0              |                       | Power supply input +3.3 V                                                               | 1 0001010    |

|     |             |                | Negative/             | Operation-in-progress signal /                                                          |              |

| 61  | #BSY/PH1    | 0              | Positive              | Excitation sequence output 1                                                            | Possible     |

| 62  | #FUP/PH2    | 0              | Negative/<br>Positive | Acceleration monitor output / Excitation sequence output 2                              | Possible     |

| 63  | #FDW/PH3    | 0              | Negative/<br>Positive | Deceleration monitor output /Excitation sequence output 3                               | Possible     |

| 64  | #MVC/PH4    | 0              | Negative/<br>Positive | Constant speed monitor output<br>/Excitation sequence output 4                          | Possible     |

| 65  | ELL         | 1              | FUSITIVE              | Set ±EL input logic                                                                     | Possible     |

| 66  | GND         | Ι <sub>υ</sub> |                       | GND                                                                                     | FUSSIBle     |

| 67  | #MSEL       | 0              | Negative              | Goes LOW for a certain interval while this chip is sending/receiving data.              | Possible     |

| 68  | #MRER       | 0              | Negative              | Goes LOW for a certain interval when<br>an abnormal communication has been<br>received. | Possible     |

| 69  | #TOUT       | 0              | Negative              | Watchdog timer output                                                                   | Possible     |

| 70  | BRK         | I <sub>D</sub> | Positive              | Break frame send request                                                                | Possible     |

| 71  | TUD         | Ι <sub>U</sub> |                       | Select operation method for outputting watchdog timer signal                            | Possible     |

| 72  | TMD         | Ιυ             |                       | Watchdog timer setting                                                                  | Possible     |

| 73  | VDD         |                |                       | Power supply input +3.3 V                                                               |              |

| 74  | CLK         |                |                       | Reference clock                                                                         |              |

| 75  | GND         |                |                       | GND                                                                                     |              |

| 76  | CKSL        | Ιυ             |                       | Select clock rate                                                                       | Possible     |

| 77  | SPD0        | ιυ<br>Ιυ       |                       | Communication speed setting 0                                                           | Possible     |

| 78  | SPD1        | ιυ<br>Ιυ       |                       | Communication speed setting 1                                                           | Possible     |

| 79  | GND         | υ              |                       | GND                                                                                     | 1 0331016    |

| 80  | #RST        | Ιυ             | Negative              | Reset                                                                                   | Possible     |

|     |             |                |                       | NESEL                                                                                   |              |

Note 1: "I" in the I/O column expresses input, "O" as output, and "B" as both directions.

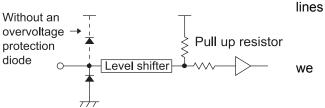

Note 2: All the inputs, including bi-directional signals can be interfaced with 5 V lines. They can be connected to 5 V CMOS, 3.3 V CMOS, TTL, and LVTTL devices. All the outputs, except the outputs related to communications (including bi-directional signals), can be interfaced with 5 V lines. They can be connected to 3.3 V CMOS, TTL, and LVTTL devices. To connect a 5 V CMOS device, connect pull up resistors (5~10K ohms) to +5 V.

Note 3: Inputs that can be interfaced with 5 V are not equipped with an overvoltage prevention diode for the 3.3 V lines. If overvoltage is possible due to a reflection, linking, or to inductive noise, recommend inserting a diode to protect against overvoltage.

Note 4:  $I_{U}$  and  $B_{U}$  in the table indicate

terminals with a pull up resistor to prevent floating. " $I_D$ " indicates terminals with a pull down resistor to prevent floating. The inputs that can be connected to 5 V lines are not connected directly to pull up/pull down resistors (a few 10K-ohms to a few 100 k-ohms). They are connected after a level shifter.

If you want to drive these terminals using an open collector, you must connect pull up resistors (5~10K-ohms) externally.

Input terminals that are not used and which have internal pull up/ pull down resistors can be left open. However, we recommend pulling these unused terminals up to 3.3 V externally, or connect them directly to the 3.3 V or GND terminals.

- Note 5: Leave the unused output terminal's open.

- Note 6: "Negative" and "Positive" in the logic column mean negative logic and positive logic. In addition, a "#" means that the terminal's logic can be changed with software. A "%" means that the terminal's

logic setting can be changed by another terminal. The logic shown in the <sup>table</sup> is the default condition. The DIR terminal logic shown is when it is used in Two-pulse mode.

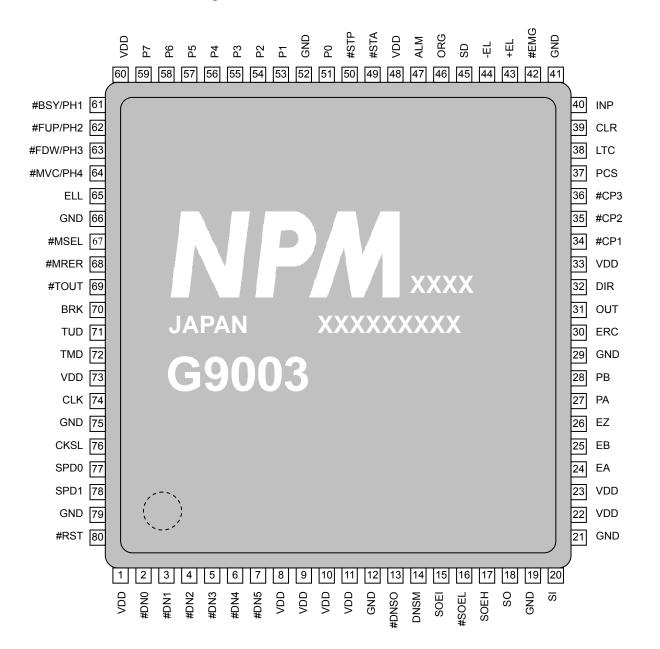

### 4-2. Terminal allocation diagram

Note: As you can see in the figure above, pin number 1 is to the lower left of the LSI model name marked on the chip.

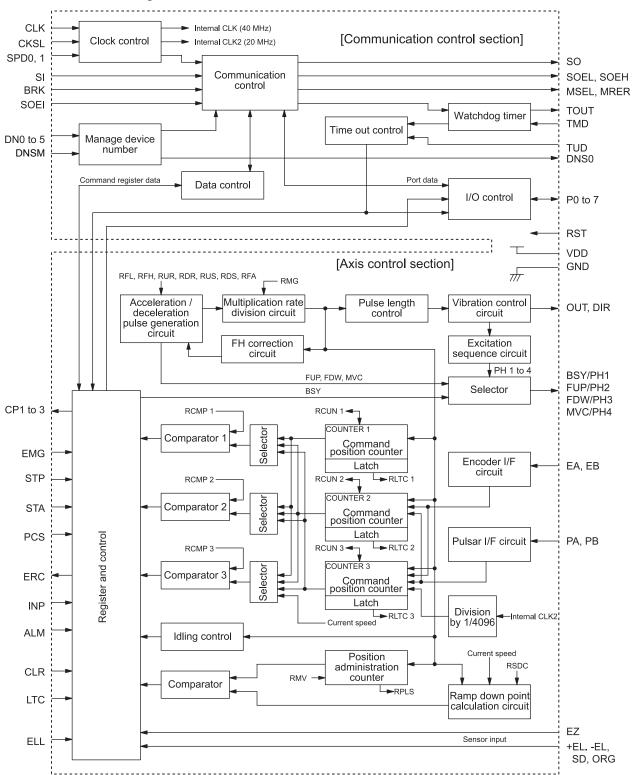

## 4-3. Entire block diagram

## 4-4. Functions of terminals

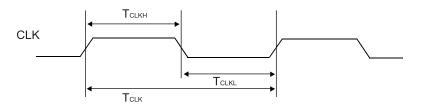

#### 4-4-1. CLK

This is an input terminal of the reference clock. By setting the CKSL terminal, either of the following clock rate signals can be connected.

CKSL = L: 40 MHz CKSL = H: 80 MHz

By selecting either of these clock rates, the serial communication transfer rate does not change. This clock rate selection affects communication precision.

For a small-scale serial communication and transfer rate below 10 Mbps, use of the center device with 40 MHz does not give any restriction.

With 20 Mbps transfer speed; however, a longer communication line or a large number of connected local devices may deteriorate communication precision due to collapse of signals on the circuit. This deterioration of communication quality can be corrected inside the LSI if the deterioration level is not much. In order to improve correction precision; however, evenness of the clock duty is required. In other words, if the duty is ideal (50:50), the capacity to correct collapse of the signals in the communication lines can be improved. On the contrary, if the duty is not ideal, the center device cannot cope with collapses of the communication line.

As a result, if the duty is close to ideal, the center device can be used with 40 MHz. When connecting more than one oscillator, the duty will not be ideal. In this case, select 80 MHz. The center device divides the frequency inside and creates 40 MHz frequency.

If you do not want to use 80 MHz frequency, you may prepare a separate 40 MHz oscillator for this LSI. The CLK terminal cannot be connected to 5 V. Supply only a 3.3 V CMOS level signal to the CLK terminal

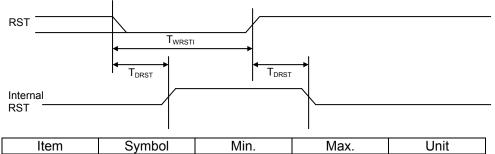

#### 4-4-2. #RST

This is an input terminal for a reset signal.

By input L level signal, the center device is reset. As the center device synchronizes with a clock, arrange a circuit so that it does not disconnect the clock while resetting. Longer than 10 clock cycles is required during resetting.

#### 4-4-3. CKSL

Use to select clock rate.

L: Connect 40 MHz clock frequency to the CLK terminal.

- H: Connect 80 MHz clock frequency to the CLK terminal.

- Select this when the duty of the 40 MHz clock collapses a lot.

#### 4-4-4. #DN0 to #DN5

Input terminals for setting device address.

Since these terminals use negative logic, setting all the terminals to LOW calls up device address "3Fh." There are two methods for entering a device address. Select the input method using the DNSM terminal.

#### 4-4-5. DNSM

Select the input method for loading the device address.

1) When the DNSM = H

Specify an address from 00h to 3Fh using the #DN0 to #DN5 terminals.

2) When the DNSM = L

Input a #DNSO signal that is output by some other chip on the #DN0 terminal on this device. When using this input method, this chip has an address equal to the other chip's address plus one. When using this method, connect terminals #DN1 to #DN5 to GND.

When two sequential sets of serial data match, the data is taken to be a device address.

#### 4-4-6. #DNSO

The numeric equivalent of the address on #DN0 to #DN5 + 1 will be output after being converted into a serial bit stream.

Connect this output to another local device's #DN0 terminal (make all the other DNSM terminals of that local device LOW), so that other devices can get the address and pass it along to the next data-sending device.

Please note that the next address after "3Fh" (#DN(5:0) = " 000000") is "00h."

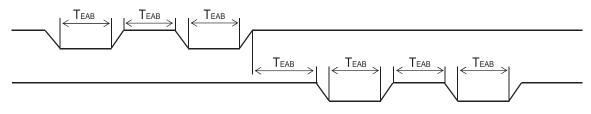

In the case that continuous address by #DNSO signal is set, it is necessary to have at least approximately 50 µs until the next address is confirmed.

#### 4-4-7. SPD0, SPD1

Set the communication speed

All of the devices on the same communication line must be set to the same speed.

| SPD1 | SPD0 | Communication speed |

|------|------|---------------------|

| L    | L    | 2.5 Mbps            |

| L    | Н    | 5 Mbps              |

| H    | L    | 10 Mbps             |

| H    | Н    | 20 Mbps             |

#### 4-4-8. TUD

A watchdog timer is included on the chip to assist in administration of the communication status (see the "TMD" terminal section).

When the data transmission interval from a center device to this device exceeds the set time, the watchdog timer times out.

This terminal is used to set output conditions when the watchdog timer times out.

When TUD = HIGH --- The LSI keeps its current status.

When the TUD = LOW --- Reset I/O port output, and immediately stops pulse output (stop operation).

#### 4-4-9. TMD

Specify the time for the watchdog timer.

The watchdog timer is used to administer the communication status.

When the interval between data packets sent from a center device is longer than the specified interval, the watchdog timer times out (the timer restarts its count at the end of each data packet received from a center device). The time out may occur because of a problem on the communication circuit, such as disconnection, or simply because the center device has stopped communicating. The time used by the watchdog timer varies with communication speed selected.

| TMD terminal | Watchdog timer setting |         |        |          |  |  |  |

|--------------|------------------------|---------|--------|----------|--|--|--|

| TMD terminal | 20 Mbps                | 10 Mbps | 5 Mbps | 2.5 Mbps |  |  |  |

| L            | 5 ms                   | 10 ms   | 20 ms  | 40 ms    |  |  |  |

| Н            | 20 ms                  | 40 ms   | 80 ms  | 160 ms   |  |  |  |

#### 4-4-10. #TOUT

Once the watchdog timer has timed out, this terminal goes LOW.

#### 4-4-11. SO

Serial output signal for communication. (Positive logic, tri-state output)

#### 4-4-12. SOEH, #SOEL

Output enable signal for communication. The difference between the SOEH and #SOEL is that the logic is inverted. When sending, SOEH = HIGH and #SOEL = LOW.

#### 4-4-13. SOEI

When using more than one PCL device, connect the SOEH signal of the other PCL device (G9003) to this terminal.

By being wire OR'ed with the output enable signal from this PCL device (G9003), the device outputs an enable signal to SOEH or #SOEL.

#### 4-4-14. SI

Serial input signal for communication. (Positive logic)

#### 4-4-15. #MRER

Monitor output used to check communication quality. When the PCL device (G9003) receives an error frame such as a CRC error, this terminal goes LOW for exactly 128 CLK cycles (3.2  $\mu$ s).

By timing this interval using a counter, you can check the quality of the communication.

#### 4-4-16. #MSEL

Communication status monitor output.

When the PCL device (G9003) receives a frame intended for this device and everything is normal (when communication MFER is OFF), this terminal goes LOW for exactly 128 CLK cycles (3.2  $\mu$ s). This can be used to check the cyclic communication time.

#### 4-4-17. BRK

By providing HIGH pulses that are longer than the specified interval, the PCL device (G9003) will be made to wait for a break frame.

When the PCL device receives a break frame send request from a center device, it immediately sends a break frame.

The break frame is 60 bits long.

A pulse at least 3200 µsec long is needed, in order to be seen as the BRK input pulse (positive logic).

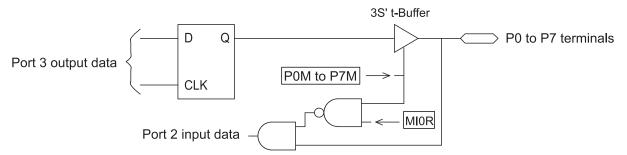

#### 4-4-18. P0 to P7

Using software, these terminals can be set to function as general-purpose input or output terminals. These terminals have built-in pull up resistors to prevent floating. When not used, they can be left open. However, if you want to improve the noise resistance of the chip, pull them up (5 to 10 K-ohms).

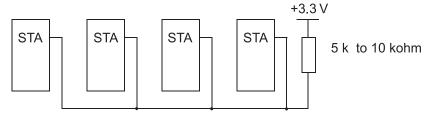

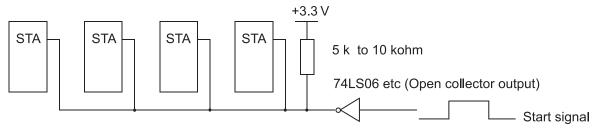

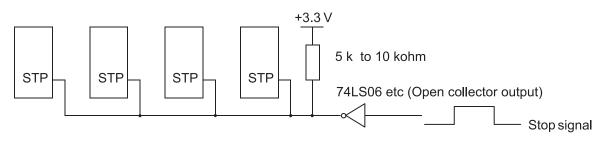

#### 4-4-19. #STA, #STP

If you want to start multiple LSI devices simultaneously, connect the #STA terminals of all the LSI devices together.

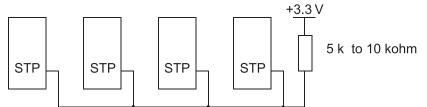

If you want to stop multiple LSI devices simultaneously, connect the #STP terminals of all the LSI devices together.

These terminals have built in pull up resistors to prevent floating. When not used, they can be left open. However, if you want to improve the noise resistance of the chip, pull them up (5 to 10 K-ohms).

#### 4-4-20. #EMG

This is the emergency stop input terminal.

While this is set LOW, the PCL device (G9003) prohibits operation. If this signal goes LOW while the motor is operating, the motor will stop immediately.

This terminal has a built in a pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-21. ELL

This terminal is used to set the input logic of the +EL and -EL signals. When this terminal is LOW, the respective signal is set for positive logic.

#### 4-4-22. +EL, -EL

Provide the stroke end signals to these terminals. Their input logic can be changed using the ELLn terminals.

When this signal (for the feed direction) turns ON, the motor stops immediately, or decelerates and stops, depending on the conditions.

These terminals have built in pull up resistors to prevent floating. When not used, they can be left open. If you want to improve the noise resistance of the chip, pull them up (5 to 10 K-ohms) or connect them to VDD

#### 4-4-23. SD

Input for the deceleration signal (decelerate and stop). Software can be used to change the input logic of this terminal.

This input has a latch function.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-24. ORG

Input for an origin return signal. Software can be used to change the input logic of this terminal. This input has a latch function.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-25. ALM

Input for an alarm signal. Software can be used to change the input logic of this terminal. When this signal turns ON, the motor stops immediately, or decelerates and stops, depending on the conditions.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-26. OUT, DIR

While the PCL device (G9003) is in the common pulse mode, it sends feed pulses from the OUT terminal, and supplies a direction signal from the DIR terminal. While the PCL device (G9003) is in the Two-pulse mode, it outputs positive direction feed pulses from the OUT terminal, and negative direction feed pulses from the DIR terminal.

#### 4-4-27. PA, PB

Used to operate the motor from external pulses, such as a manual pulsar. 90 phase difference signals or Two-pulses (up pulse and down pulse) can be supplied to these terminals. The 90 phase difference signals can be multiplied by 2 or by 4.

These terminals have built in pull up resistors to prevent floating. When not used, they can be left open. If you want to improve the noise resistance of the chip, pull them up (5 to 10 K-ohms) or connect them to VDD

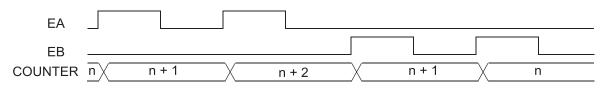

#### 4-4-28. EA, EB, EZ

Use these terminals to control the current position using an encoder.

90 phase difference signals or Two-pulses (up pulse and down pulse) can be input on these terminals. The 90 phase difference signals can be multiplied by 2 or by 4.

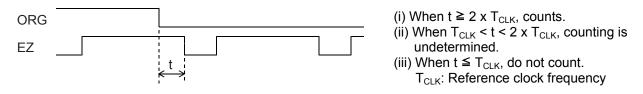

The EZ input is used for origin return operations. Software can be used to change the input logic of these terminals. These terminals have built in pull up resistors to prevent floating. When not used, they can be left open. If you want to improve the noise resistance of the chip, pull them up (5 to 10 K-ohms) or connect them to VDD.

#### 4-4-29. PCS

The PCL device (G9003) starts positioning control. (Override 2 of the target position) when a signal is applied to this terminal.

Software can be used to change the input logic of this terminal.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open.

However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-30. INP

Input for a positioning-complete signal from a servo driver.

The output of the INT can be delayed until this signal is input.

Software can be used to change the input logic of this terminal.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open.

However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-31. CLR

Reset the specified counter (COUNTER1 to 3) by inputting a signal (can be used to reset more than one counter).

Software can be used to change the input logic of this terminal.

This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

#### 4-4-32. LTC

Latch the specified counter (COUNTER1 to 3) by inputting a signal (can latch more than one counter). Software can be used to change the input logic of this terminal. This terminal has a built in pull up resistor to prevent floating. When not used, it can be left open. However, if you want to improve the noise resistance of the chip, pull it up (5 to 10 K-ohms), or connect it to VDD.

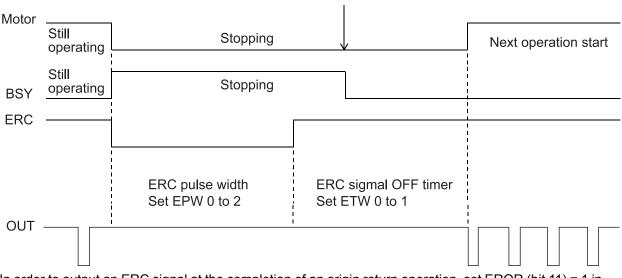

#### 4-4-33. ERC

Outputs a one-shot pulse to clear a deflection counter for a servo driver. The output logic and pulse length can be set using software. (A level output is also possible.) If this terminal is not used, leave it open.

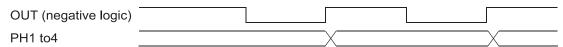

#### 4-4-34. #BSY/PH1

When #BSY is selected, the PCL device (G9003) outputs a LOW while the motor is operating. When PH1 is selected, the PCL device (G9003) outputs an excitation sequence for a 2-phase stepper motor.

Select #BSY/PH1 using the RMD register. If this terminal is not used, leave it open.

#### 4-4-35. #FUP/PH2

When #FUP is selected, the PCL device (G9003) outputs a LOW while the motor is accelerating. When PH2 is selected, the PCL device (G9003) outputs an excitation sequence for a 2-phase stepper motor.

Select #FUP/PH2 using the RMD register.

If this terminal is not used, leave it open.

#### 4-4-36. #FDW/PH3

When #FDW is selected, the PCL device (G9003) outputs a LOW while the motor is decelerating. When PH3 is selected, the PCL device (G9003) outputs an excitation sequence for a 2-phase stepper motor.

Select #FDW/PH3 using the RMD register. If this terminal is not used, leave it open.

#### 4-4-37. #MVC/PH4

When #MVC is selected, the PCL outputs a LOW while the motor is fed at a constant speed. When PH4 is selected, the PCL outputs an excitation sequence for a 2-phase stepper motor. Select #MVC/PH4 using the RMD register. If this terminal is not used, leave it open.

#### 4-4-38. #CP1

When the conditions for Comparator 1 are met, the PCL device (G9003) outputs a LOW on #CP1. If this terminal is not used, leave it open.

#### 4-4-39. #CP2

When the conditions for Comparator 2 are met, the PCL device (G9003) outputs a LOW on #CP2. If this terminal is not used, leave it open.

#### 4-4-40. #CP3

When the conditions for Comparator 3 are met, the PCL device (G9003) outputs a LOW on #CP3. If this terminal is not used, leave it open.

## 5. Description of the software

#### 5-1. Outline of control

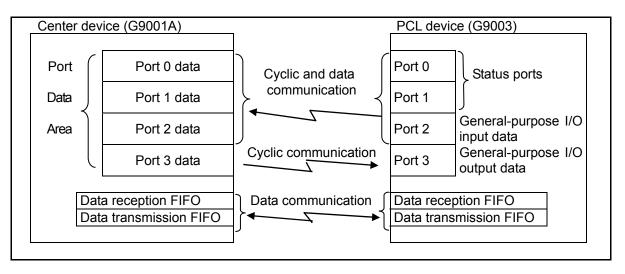

#### 5-1-1. Communication control

- The center device (G9001A) controls all the communication.

- One communication cycle consists of a communication from the center device to the local devices, and the communication from the local devices back to the center device.

- The response from the local devices may include I/O information and data.

- This PCL device (G9003) is a local device.

#### 5-1-2. Communication type

System communications, cyclic communications, and data communications are the three communication types available.

1) System communications

With the system communications, the center device automatically confirms the connection status, device type, and I/O port settings of each local device.

By starting the system communication, the center device polls all of the local devices (device No. 0 to 63), one by one, and refreshes the "device information" area according to the response from the local devices.

#### 2) Cyclic communication

In cyclic communication, the center device communicates continuously to perform I/O control of the I/O devices. This communication takes place in cycles. (Communication starts with the local device that has the lowest device number and proceeds through all the devices that are present. When the communication with the device that has the highest number is complete, the center device again starts to communicate with the local device that has the lowest device number.) If the communication target is a data device, it exchanges information such as device status.

By writing a cyclic communication start command, the center device communicates only with devices whose "device information" bit is set to 1.

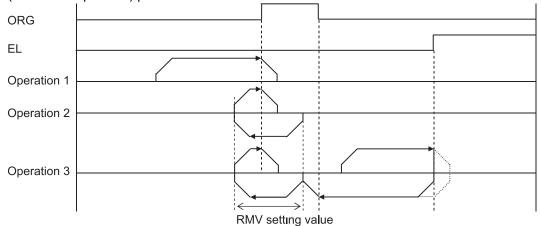

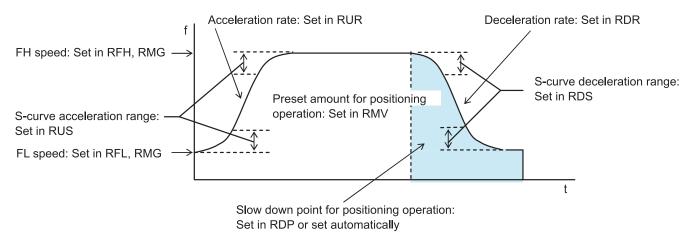

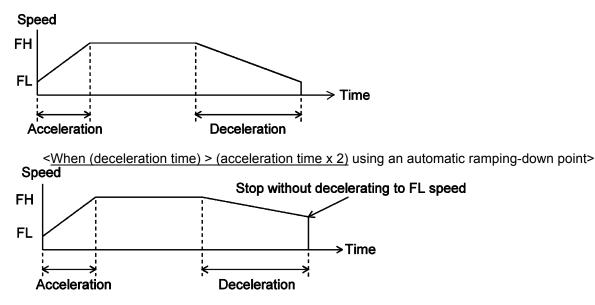

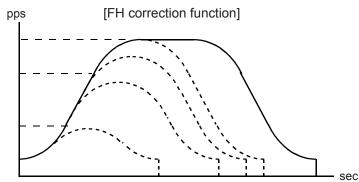

This communication continues until a cyclic communication stop command is written.